用非傳統MOSFET方案提高功率CMOS器件的功效

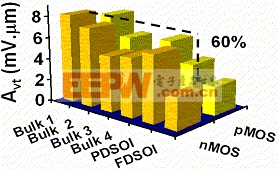

取消溝道摻雜也減少了因隨機摻雜物波動引起的可變性。盡管在薄Si體厚度中有變化,與有摻雜體器件相比,FD-SOI器件顯示非常大地改進了器件與器件之間的匹配性能 (圖8)。這對于存儲容量不斷擴大的SRAM和受隨機變化影響的模擬技術而言則是非常重要的。

圖8: FD-SOI與其它來自不同工藝的等效器件之間的失配比較(PDSOI:部分損耗的SOI)。

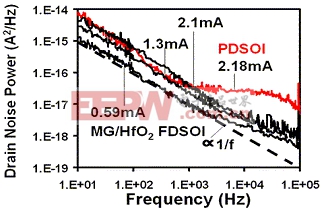

FD-SOI對浮體效應的免疫性和最小化源/漏(S/D)結電容(Cj)以及跟金屬門柵和高K電介質的結合,為低功耗和混合信號應用提供了多種優點,這些優點包括降低的門漏電、良好的線性及低噪音[3](圖9)。

圖9:與PDSOI器件相比,FD-SOI 器件顯示出更低的噪音。

應變硅與增強傳輸特性

通過改善短溝道靜電的影響,降低了漏電、可變性及待機功耗。在某種程度上,它甚至改進了傳輸特性。然而, 要充分地降低動態功耗,而不必對漏電和性能作出折衷,就需要進一步增強傳輸特性。

由于動態功耗的二次方程式取決于Vdd (CVdd2F), 調整電源電壓是降低動態功率的最有效的方法。然而,如果門限電壓并沒有降低, 那么,Vdd的減少會導致晶體管中載流子密度(Qi)的大量損耗。

Qi(max) ~ Cox (Vdd-VT)

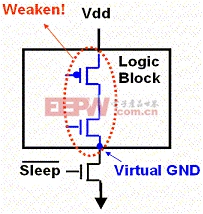

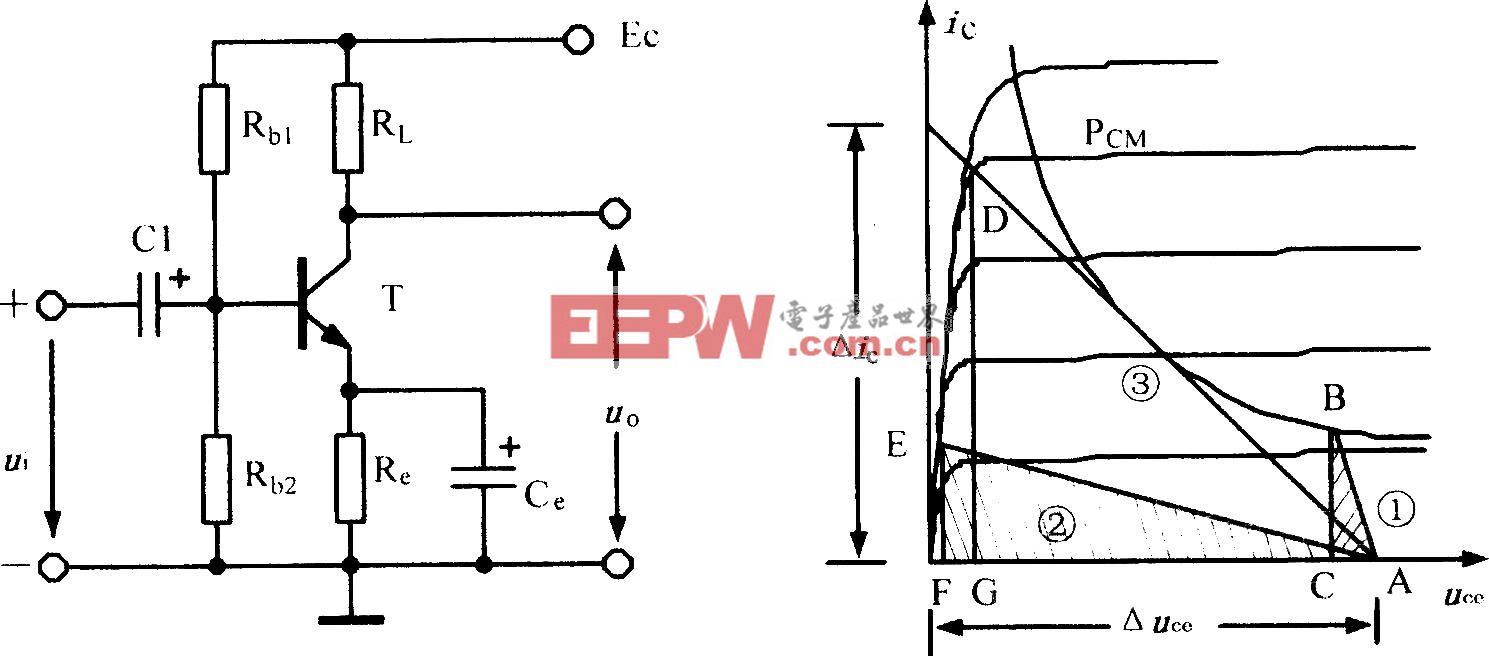

由于源/漏漏電呈指數地依賴于VT(圖2), 要調整VT就變得十分受到限制。此外,Cox的增加受到Tox的限制, 這一點最終受到門漏電和電介質可靠性的限制。 當晶體管被堆疊以減少漏電時,一個類似的問題又出現了(圖10)。在邏輯模塊中的堆疊器件要減少其最大門柵過驅動的虛擬節點(Vdd'-VT),因此,它們會隨著堆疊的增加變得更加弱。

圖10:晶體管堆疊對于實現“休眠”晶體管和電源門控技術已很常見。

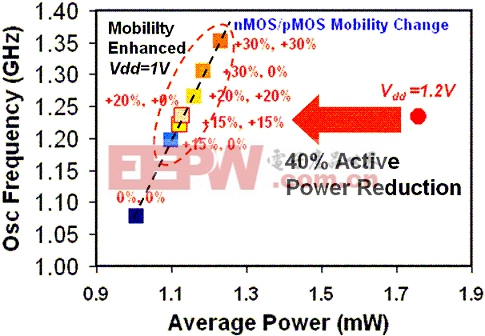

要恢復相同的電流(I=Qi速率),載流子速率(或遷移率)必須得到增加以彌補Qi損耗。這正是遷移率隨應變硅的優越而得到增強之處。

隨著英特爾宣布,把應力襯底材料和SiGe源/漏的結合進入90nm 技術節點,針對不同工藝的應變硅已應用到產品之中,被集成以增強他們的CMOS器件[4]。此外,人們還研究了從雙壓力襯底到襯低應變硅的許多其它的方法。推動晶體管性能的根本目標是相同的:實質性地增強遷移率,我們能在維持電路性能的同時,為降低動態功耗,而對驅動電流進行折衷(圖11)。

圖11: 振蕩器電路模擬表明:在保持頻率性能的同時提高遷移率,通過把Vdd從1.2V 降到1V,可以減低平均功耗。

這就意味著提高遷移率?傳統的高性能晶體管的發展推動力?也開始向低功耗管理這個前沿轉移,因此,要研究獲得更高遷移率的縮放路徑。

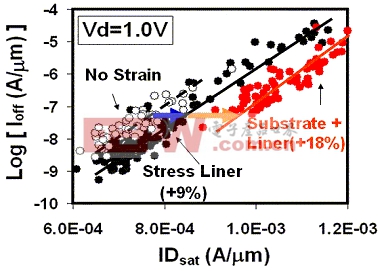

通過工藝技術把現有各種應力材料的優勢結合起來并加以增強,是進一步提高性能的自然方法(圖12, 13) [5]。最終,除了應變硅外,可能還需要具有更高遷移率的非硅材料,從而引領工藝及設計工程師努力開發新工藝并解決各種設計復雜性問題。

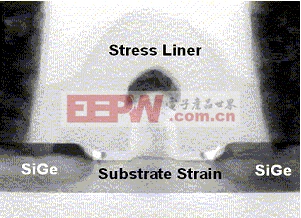

圖12:直接制作在在絕緣體上的應變硅(襯底應變)與嵌入式SiGe源?漏及襯底應力材料的結合,可以實現混合應變PMOSFET。

圖13:由應力襯低結合的絕緣體(襯底應變硅)上直接制作的應變硅增強了的NMOSFET性能。

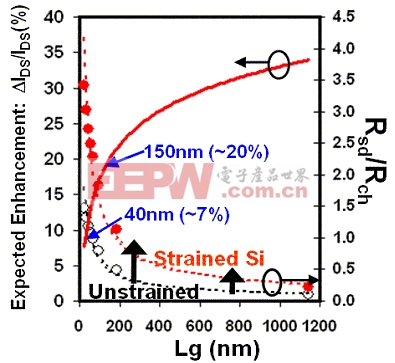

提高遷移率終于獲得了成功? Lg和溝道遷移率的提升加速了晶體管溝道阻抗(Rch)的降低,而寄生源/漏和接觸電阻(Rsd)要以更慢的速度降低。由于寄生參數導致越來越多的電壓降,增加Rsd/Rch比率會導致逐漸抵消所增強的晶體管性能,盡管遷移率增加(圖14)[6]。這就意味著,要把寄生電阻急劇降低的新型工藝與提高遷移率同時開發,以避免相互抵消。

圖14:因遷移率增強,驅動電流增強及作為Lg應變硅函數之一的Rsd/Rch加速了Rsd/Rch的增長,導致返回的驅動電流逐漸減小。

本文小結

我們發現日益改進的靜電學及晶體管傳輸有助于形成一種成熟的方法,這種方法能夠降低有源和待機功耗。要做到這一點,新型晶體管結構和材料拓展了性能?功耗設計空間,使之超躍了傳統的本體硅晶體管。最終,通過構成一個由多層系統-電路-器件電源管理生態系統構成的底層,晶體管的創新將會繼續在定義下一代提高功效的策略時發揮關鍵作用。

評論