基于FPGA和BU-65170的1553B遠程終端設計與實現

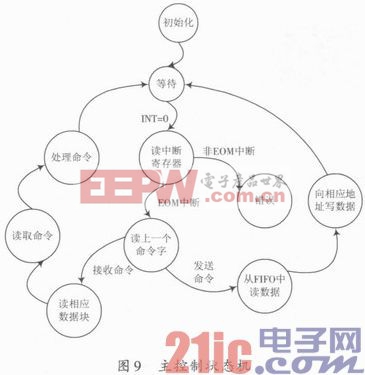

3.5 主控制器

FPGA中控制與BU-65170通信的主控制狀態機如圖9所示。初始化完成后程序進入等待狀態。此時如果收到中斷信號(INT=0),則首先讀取中斷寄存器,判斷是否為消息結束中斷(EOM),如果不是,進入錯誤狀態,等待BC對RT進行檢查或重啟RT;如果是消息結束中斷,則繼續讀取上一個命令字,若是發送命令,則從FIFO中讀取28 B的狀態信息數據,接著向相應的發送子地址數據塊填寫數據,在RT收到下一個發送命令后,BC從相應子地址讀取上一條數據,這與對BU-65170進行讀操作的原理相似。如果上一個命令字是接收命令,則讀取相應子地址對應的數據塊,然后讀取具體命令內容,再根據命令進行相應的處理,最后回到等待狀態。本文引用地址:http://cqxgywz.com/article/189492.htm

接收子地址1工作在雙緩沖模式,用于接收BC發送的廣播時間碼,加載到每一條從RT發送到BC的狀態信息的頭部。雙緩沖模式可以使FPGA訪問指定子地址剛接收到的消息,RT將接收的數據字交替存儲到數據塊0和數據塊1中。當FPGA需要訪問接收子地址1內的消息時,首先將其改成單消息模式,讀取數據塊地址,并將其bit5的值取反得到“非活躍”數據塊的地址,讀取其上的最新時間碼后再將接收子地址1改為雙緩沖模式。

4 測試

選用Alta公司的ECD54-1553多功能板卡(能模擬BC\RT\BM)作為BC,與設計的RT搭成一個測試系統,如圖10所示。

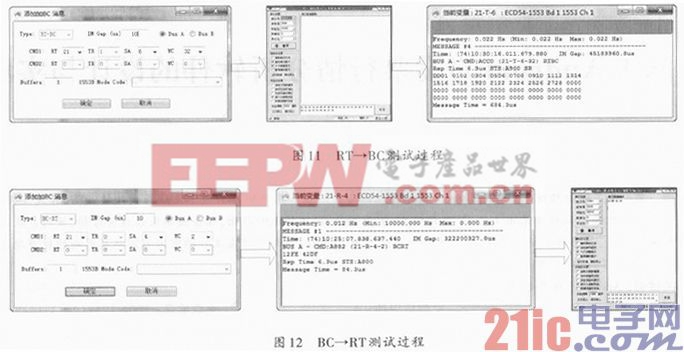

首先在ECD54-1553的控制界面中設置RT地址為21,然后根據在FPGA邏輯中設定的RT子地址及傳輸數據量進行相應的設置,再開啟總線監控(BM)功能,測試RT→BC的過程如圖11所示。設置RT地址為21、發送子地址為6、數據量為32個字(2 B標志位+28 B數據+2 B保留位);通過串口調試助手從PC機向RS 422發送28 B數據;經過FPGA處理后傳送給1553B總線控制器,BM顯示總線控制器正確收到從RS 422發來的數據。測試BC→RT的過程如圖12所示。

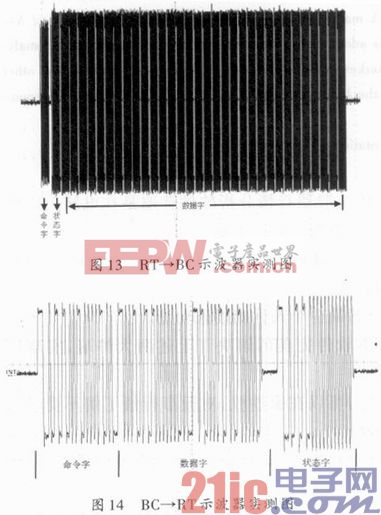

設置RT地址為21、接收子地址為4、數據量為2個字;由BC發送2個字的數據12FE 42DF;串口調試助手顯示RS 422正確接收到BC發送過來的數據。示波器測得的實際曼徹斯特Ⅱ型碼波形如圖13,圖14所示。

測試結果表明RT能正確、穩定地跟BC進行通信,達到工程項目所需的要求。

5 結語

本文設計了基于FPGA和BU-65170的1553B遠程終端,實現1553B通信。詳細介紹了硬件連接、BU-65170芯片配置、FPGA邏輯模塊、UART設計、測試過程和結果。通過引入RS 422接口,更加直觀地觀測到1553B通信過程,易于調試。采用FPGA的最大優點是能迅速移植代碼,縮減研發周期。隨著技術的發展,對數據傳輸和處理提出了更高的要求,未來可以把控制其他子系統的模塊和數據處理功能集成在一塊FPGA芯片中提高集成性,便于開發和維護。

fpga相關文章:fpga是什么

評論