FPGA工程師應如何挑選ADC和DAC

DAC濾波

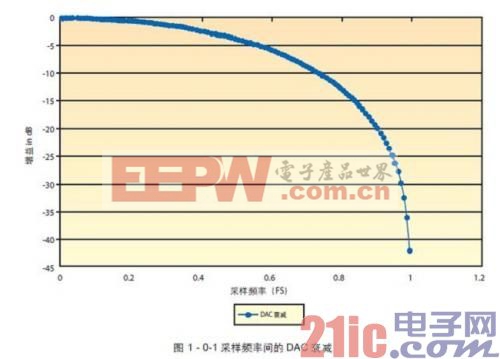

大多數DAC一直將模擬輸出保持到下一個采樣周期,這將對輸出頻率域產生良好的效果。用戶將注意到這兩個圖像均存在于整個輸出頻譜中,由于在0.5FS時正弦效應將接近4dB(3.92dB),所有奈奎斯特區域中的輸出信號都出現衰減(如圖1所示)。這兩大問題均可利用濾波器來解決。

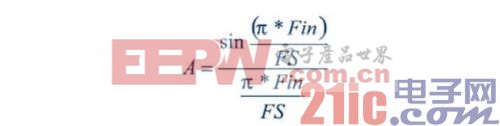

用戶可以像實現FIR濾波器一樣輕松實現正弦校正濾波器。開發該濾波器最簡單的方法就是利用下列方程式來繪制正弦衰減特性。

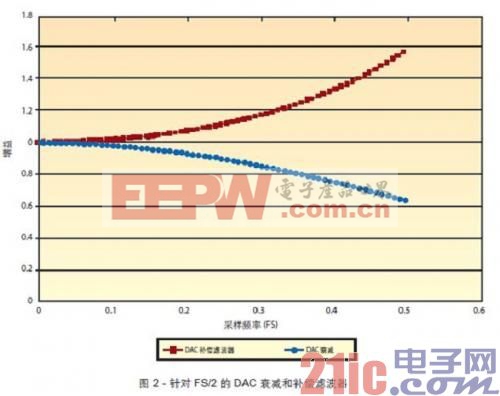

先創建校正因子,該因子是所計算出衰減系數的倒數,然后再執行逆傅里葉變換,以獲取所需要設計濾波器的系數。通常情況下,用戶需要采用幾個抽頭才能實現該濾波器。表2給出了濾波器的前11個系數,同時圖2還給出了針對衰減的補償。

在系統測試

眾多這類系統都將利用轉換器實現終端應用的具體性能特征,如CDMA或GSM等。為實現該項性能而進行的測試需要在測試系統(任意波形生成器、邏輯分析儀、模式生成器、頻譜分析儀等)方面進行大量的投入。但是,FPGA高度的可重編程靈活性使用戶能將特定的測試程序插入至器件中,這樣既可以捕獲并分析ADC的輸出也可以提供DAC激勵,從而減少對更多額外測試設備的需要。

轉換101

由于FPGA通常需要與ADC和DAC接口相連,因而對于任何FPGA工程師來說,基本了解這些器件參數的重要性非常關鍵。如果用戶計劃在設計驗證與調試過程中利用FPGA的可重編程靈活性來測試轉換器的性能,這一點尤其有用。

模擬信號相關文章:什么是模擬信號

fpga相關文章:fpga是什么

模數轉換器相關文章:模數轉換器工作原理

脈寬調制相關文章:脈寬調制原理

評論