基于FPGA的水聲信號采樣存儲系統設計

3 系統整體設計

3.1 硬件邏輯設計

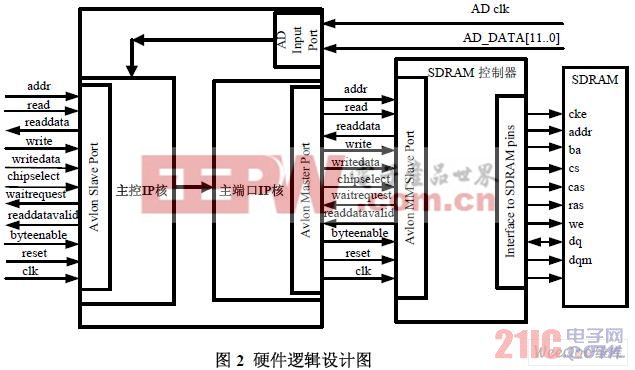

硬件邏輯設計主要包括主控IP 核設計與主端口IP 核設計兩部分工作,分別實現對于 AD 采樣數據的存儲和讀取時序控制,以及AVALON 總線的主端口建立的目的。硬件邏輯 利用IP 核模塊化,移植性好的特點,方便整合到傳感器節點的整體設計當中。作為傳感器 節點的組成部分,為水聲通信試驗的順利進行提供可靠保證。 硬件邏輯設計圖,如圖 2 所示。

3.1.1 SDRAM 主控IP 核設計

主控IP 核通過對于QuartusII 自帶的SDRAM 控制器進行控制,實現變速率AD 采樣的 功能,以及讀寫SDRAM 的邏輯功能。由于SDRAM 控制器實現了對于SDRAM 芯片的時 序操作,所以讀寫時序設計是針對SDRAM 控制器進行[3]。

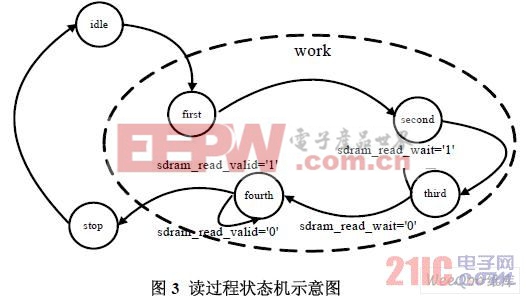

系統讀 SDRAM 操作分為數據飛讀與數據環形讀取兩種功能[4]。其中,數據飛讀是將當前AD 采樣值送回至CPU,并通過串口返回到前置機,方便實時數據監控。對于數據環形 讀取SDRAM 操作,通過設置首地址指針寄存器,在每次寫操作之后自動加一,實現環形 存儲水聲通信數據的目的。在每次環形數據讀取操作發起之前,預讀首地址指針寄存器,以 此為起始地址,始終讀取最新時刻的采樣存儲數據。 讀操作過程主要狀態機,如圖 3 所示。

其中 work 過程包含的獨立狀態機,由如下四部分構成:

(1)first:片選有效,讀使能有效,送讀SDRAM 地址。

(2)second:讀使能有效,滿足SDRAM 控制器讀時序要求。

(3)third:判斷sdram_read_wait 信號值,如果為1,則維持當前狀態,同時讀使能信號置位;如果為0,則進入下一狀態。

(4)fourth:判斷sdram_read_valid 信號值,如果為0,則維持當前狀態;如果為1,將讀回數據寫入讀SDRAM 數據寄存器,同時讀使能信號復位。

變速率AD 采集與數據環形存儲操作主要是由主控IP 核寫SDRAM 的過程實現。為保 持采樣時刻數據的穩定性,系統對AD 時鐘進行分頻,通過設置不同分頻寄存器,實現變速 率采樣的目的。數據環形存儲SDRAM 操作是靠每次分頻時鐘SDRAM_WRITE_CLK 的上 升沿觸發,基本時序過程與讀過程狀態機類似。系統從0 地址開始寫操作,一旦寫滿預設存 儲區域,則從下一寫時刻開始,數據寫入初始地址,以此類推,實現環形存儲操作。同時, 讀寫操作不能進行同時進行,通過讀寫選擇控制器的設置,分別按照不同狀態進行操作。

評論