基于FPGA的水聲信號采樣存儲系統設計

3.1.2 主端口IP 核

因為SDRAM 主控IP 核在NiosII 軟核CPU 總線控制下作為從端口,所以不能主動發起 讀寫操作,因此必須新建第二條AVALON 總線,設計讀寫主端口IP 核,才能實現讀寫外接 SDRAM 芯片的功能。主端口IP 核的時序操作,是對主控IP 核的時序轉接,面向SDRAM 控制器進行控制。根據讀寫使能信號不同,進行不同時序傳送。

3.2 軟件程序設計

NiosII CPU 作為軟核,可方便進行模塊化操作,具有可移植,可配置,易整合的特點。 在本設計當中,軟件設計主要實現以下五種主要功能:單點寫SDRAM,單點讀SDRAM, 數據飛讀,連續寫SDRAM,連續讀SDRAM 的功能。在程序當中留有接口,方便其他功能 整合,符合模塊化設計的要求。

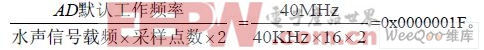

首先,完成功能的初始化,主要是設置選擇操作模式與存儲 AD 數據的時鐘分頻系數。 作為SDRAM 的讀操作必須滿足寫滿之后,方可進行,所以初始化主控IP 核為寫SDRAM 操作。設置分頻系數可以按照如下公式計算:

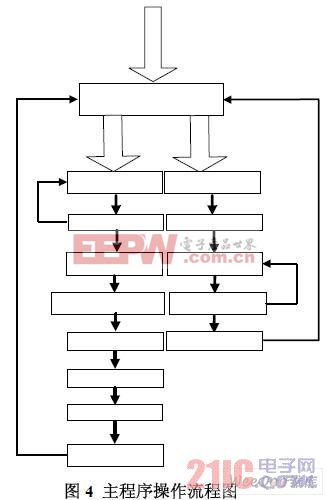

其次,通過對于串口進行協議解析,分別實現五部分預設功能。主程序操作流程如圖4所示。

實現的五部分功能依次為:

(1) 單點寫SDRAM 操作:CPU 給出地址,數據,以及寫操作選擇信號。

(2) 連續寫SDRAM 操作:CPU 只是給出寫操作選擇信號,由主控IP 核將AD 數據寫入至SDRAM 環形存儲區域內。

(3) 數據飛讀操作:只需要讀取飛讀數據寄存器,可以將當前狀態AD 輸入值送回至CPU,偵測當前狀態。

(4) 單點讀SDRAM 操作:CPU 送出讀SDRAM 地址,然后選擇讀操作,設置控制寄存器為0x00000001,啟動讀操作。最后將讀回數據通過串口實時回傳。

(5) 連續讀SDRAM 操作:是將基本讀操作進行循環執行。設置串口回傳緩沖區為80 字節,連續讀SDRAM 數據并連續填寫緩沖區,一旦填滿,則啟動串口發送。同時,讀地址在每次讀操作結束后自動加一,當操作次數達到環形空間最大存儲數量時,停止連續讀操作。

4 結束語

本設計作為水下無線傳感器網絡(UW-ASN)節點的設計組成部分,具有結構清楚,功 能完善,整合性強,性能可靠的特點。設計整體架構的模塊化操作以及可編程性,使得整個 設計開發的具有靈活性與低風險性。經項目試驗驗證,該數據采集與存儲設計滿足傳感器節 點的功能要求,為水聲通信試驗順利進行以及水下無線傳感器網絡的功能完善提供可靠保證。

本文創新點:在系統功能設計當中,充分考慮了模塊的可重用性和可移植性,通過IP核的設計實現底層驅動,提高系統集成度,充分發揮了SOPC技術的優勢。

評論