基于FPGA的寬帶數字信道化接收機的設計

2.3 FPGA應用

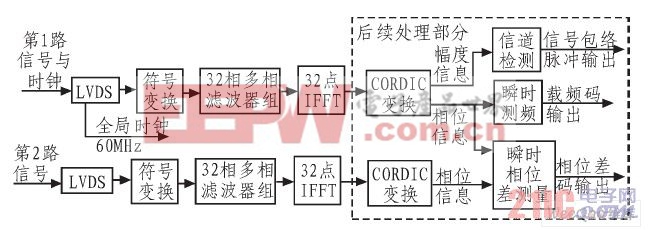

軟件模塊主要包括數字信道化過程和后續數據輸出整理兩部分。數字信道化部分主要由上述數學模型構建,包括:數據抽取、符號轉換、多相濾波和IFFT。后續數據處理主要根據信道化結果得到頻率和相位信息及對同時到達三路信號的判斷。FPGA內部處理模塊框圖如圖5所示。

圖5 FPGA內部處理模塊框圖

2.3.1 數據抽取變換

A/D輸出的240 MHz高速采樣差分信號進入FPGA。根據上述模型,若信道數K=16,則抽取倍數M=8,FPGA通過LVDS接口的串并轉換實現8倍抽取。設計采用QuartusⅡ的LNDS模塊完成信號的串并轉換,降低信號及時鐘速率。設計中將模塊設置成INDS receiver形式,選擇8倍轉換因子,可得輸出信號16組以及和A/D的隨路時鐘同步的60 MHz時鐘。用該時鐘作為全局時鐘驅動后續所有處理模塊。由于A/D采樣輸出信號為偏移二進制類型,需經符號變換模塊后變為二進制補碼類型。

2.3.2 多相濾波器的設計與仿真

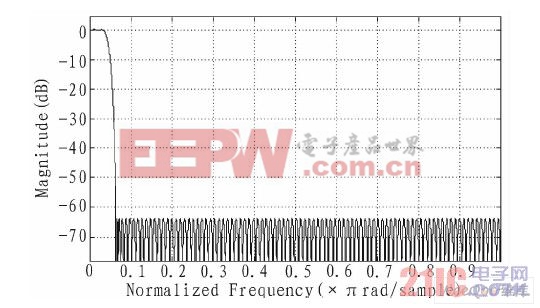

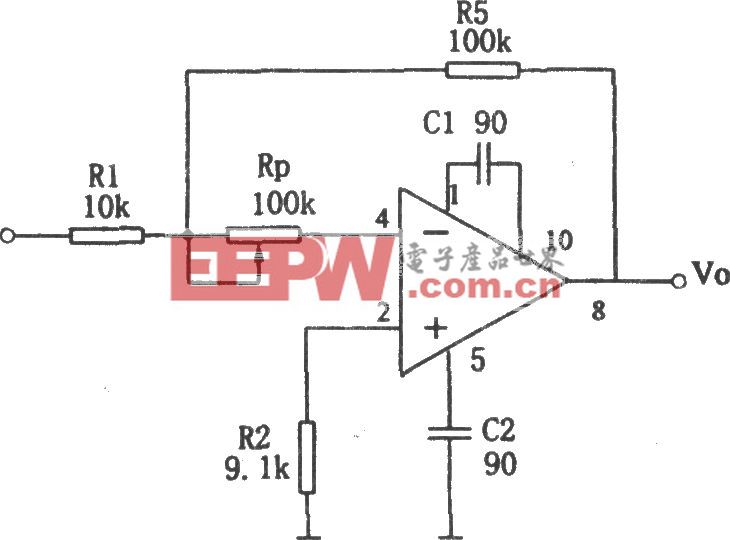

多相濾波器組采用具有穩定系統、可以實現線性相位的FIR型數字濾波器。FIR原型濾波器的設計主要考慮采樣頻率fs、通帶波紋rp、阻帶衰減rs以及過渡帶寬。例如采用fs=960 MHz,rp=0.1 dB,rs=63 dB,過渡帶起始頻率15 MHz,截止頻率30 MHz,得到原型濾波器幅頻特性曲線如圖6所示。該低通原型濾波器的階數為192階,將原型濾波器分為32相,每相濾波器為6階。由于采用50%交疊的結構需間隔插零,每相濾波器階數增至12階。設計使用程序編寫乘法累加運算實現FIR濾波。FIR原型濾波器的系數通過MATLAB生成導出,量化后寫入FPGA的濾波器程序中。

圖6 原型濾波器幅頻特性曲線

2.3.3 IFFT運算

IFFT運算采用按時間抽選的基-2算法。為了加快信號處理的速度,IFFT模塊采用多級流水線設計,并且運算模塊利用Quartus的宏產生。例如IFFT運算的核心蝶形運算可由Altmult_complex宏和lpm_add_sub宏實現。每次復數乘法會占用4個18x18 DSP乘法器資源,所以單路信道化的IFFT共需占用136個乘法器資源。

2.3.4 信道輸出

因為輸入的是實信號,經IFFT得到16個信道的子帶信號。對每個信道采用旋轉數字計算機算法(CORDIC)計算每個信道信號的幅度及瞬時相位。根據CORDIC輸出的信號幅度判斷信號是否存在以及信號的起始點和結束點,給出對應的包絡脈沖。同時利用CORDIC輸出相位根據瞬時相位差法計算頻率。為了提升測頻的準確度,用脈沖上升沿平穩后的連續4個無模糊的相位差平均值測頻,輸出載頻編碼。用兩通道信號的CORDIC輸出相位測算兩通道信號的相位差,輸出相位差編碼。

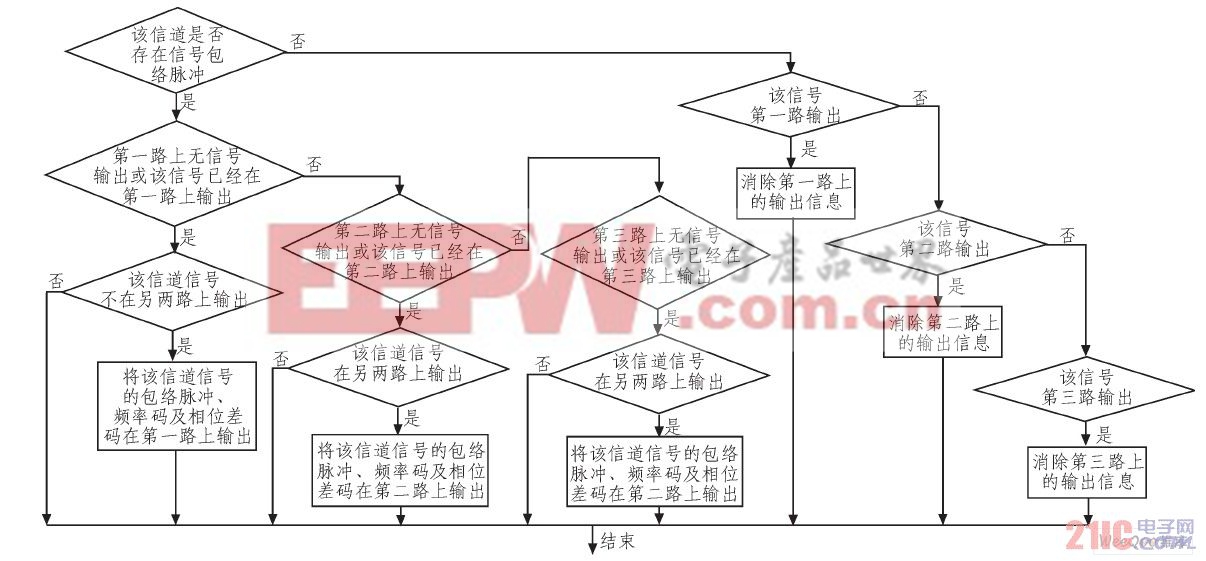

為了節省對外接口資源,最多只輸出三路信號即同時處理三路不同信號,當某路信道上出現包絡脈沖時才將該信道的頻率碼和相位差碼輸出,否則不輸出。16個信道都要進行判斷,確定是否輸出。具體流程如圖7所示,當判斷不成立或者語句執行結束時,結束程序。

圖7 輸出的判斷邏輯流程圖

3 系統硬件仿真與結果分析

本設計在EP3SE110F1152C4上完成了兩通道的信道化過程、信號包絡脈沖輸出及對載頻、相位差信息的編碼輸出。在硬件驗證仿真時,用到了內嵌式邏輯分析儀——SignalTapⅡLogic Analyzer。它是一種調試工具,能捕獲和顯示FPGA中的實時信號特性,通過JTAG接口下載FPGA配置數據和上載捕獲的信號數據,并在計算機中觀察FPGA內部節點信號,使用戶可以在整個設計工作過程中以系統級的速度觀察硬件和軟件的交互作用。FPGA芯片各項資源消耗情況如表1所示,共占用82%的資源,其中包括SignalTapⅡLogicAnalyzer所占用的資源。

表1 FPGA芯片各項資源消耗情況

A/D的采樣精度直接影響后面的精度,因此首先對A/D進行性能測試。信噪比RSN定義為信號峰值點的功率與去掉零頻以及前五階諧波分量后的所有噪聲的功率比值。信號噪聲失真比SINAD定義為信號峰值點的功率與去掉零頻后的所有諧波及噪聲的功率比值,其值較信噪比小。無雜散動態范圍SFDR定義為單信號輸入時信號與最大的諧波或雜散的功率比值。

評論