基于FPGA的寬帶數字信道化接收機的設計

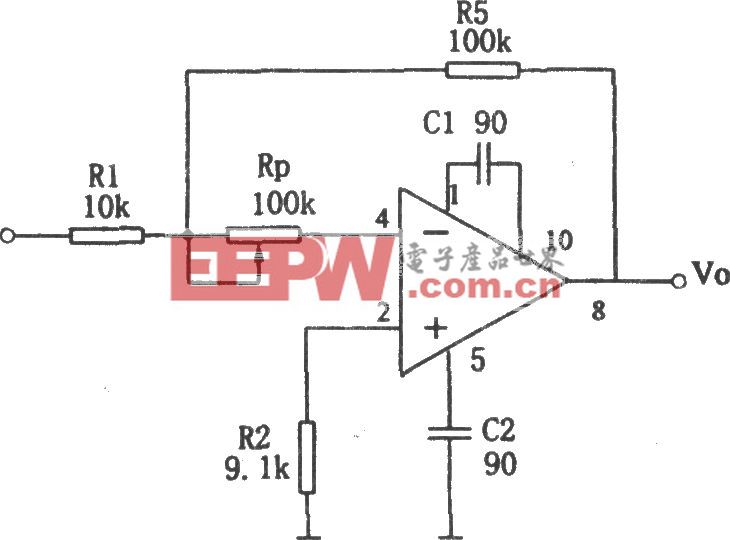

實驗四:用一臺Agilent的E4438C矢量信號發(fā)生器和兩臺Agilent的83752A作為中頻輸入,分別輸入載頻510MHz,PRI=100μs,PW=10μs;載頻為720MHz,PRI=90μs,PW=8μs;載頻為930 MHz,PRI=80μs,PW=20μs的三路脈沖信號。用示波器采集三路信號包絡脈沖輸出接口信號,可得系統對多信號處理結果如圖11所示。最上邊的線為第一路包絡脈沖輸出接口,中間的線為第二路包絡脈沖輸出接口,下邊的線為第三路包絡脈沖輸出接口。當信號在時域交疊時,由不同的輸出接口輸出包絡脈沖;否則在第一路輸出接口輸出。由圖11可以看出系統完成了對同時到達多信號的處理。

圖11 系統的多信號處理結果

4 結論

本文結合工程實際,完成了960MHz的16通道數字信道化接收機的FPGA實現。采用多相濾波器的高速高效數字信道化結構實現的數字信道化接收機,既能保證寬瞬時帶寬要求,又能達到實時處理的目的;與傳統的數字信道化結構節(jié)省硬件資源,提高系統的整體工作性能。FPGA仿真結果表明該模型在FPGA上實現的可行性以及實用性,并且實現了預期的指標要求。

評論