基于FPGA的無線信道模擬器設計

2 信道模擬器的FPGA設計

FPGA采用Xilinx公司的Virtex-2p,其中芯片工作時鐘為100MHz。本文設置N0=8,fm=200 Hz,

為了計算方便,將所得的值擴大32倍,也就是左移5位之后四舍五入成整數值,存入寄存器調用。所以信道模擬器的實現過程主要為各個正弦波的FPGA實現,與對應的系數相乘疊加成單徑衰落,輸入信號經過l個路徑時延之后疊加成為輸出信號。

2.1 正弦波的FPGA實現

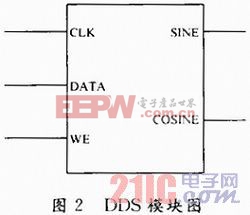

FPGA產生正弦波一般可以采用直接產生和Xilinx或者Altera利用自帶DDS的IP核例化實現。FPGA直接產生是將三角函數值存入ROM中循環調用來產生正弦波,這樣占用的邏輯資源比較少,缺點就是過程很麻煩而且不夠靈活,模型需要8種頻率的正弦波和余弦波,而且fm也可能根據需要而變化,每一次變化就需要在ROM中重新賦初值,十分麻煩。因此本文選擇調用Xilinx自帶DDS的IP核,通過邏輯資源換取效率。DDS的模塊圖如圖2所示。本文引用地址:http://cqxgywz.com/article/190237.htm

這樣,通過控制DATA的值得到所需頻率的正弦波。![]() ,其中fclk為開發工作時鐘,DATA為輸入的頻率控制字,B為DATA的位寬,fout為所得的頻率。

,其中fclk為開發工作時鐘,DATA為輸入的頻率控制字,B為DATA的位寬,fout為所得的頻率。

2.2 時延模塊的FPGA實現

輸入通過時延后與各路徑的衰落系數相乘,然后各個路徑疊加成輸出信號。本文中時延采用計數分頻來實現,如延遲1μs,工作時鐘為100MHz,所以計算100個時鐘周期后,將輸入的值存入寄存器1,再計算100個時鐘周期后將輸入值存入寄存器2,依次類推,本為路徑l設置為5,所以最終有5個寄存器存放輸入值。

2.3 測試模塊的FPGA實現

最后需要將算得的數據上傳到Matlab進行統計分析,所以還需要FPGA串口驅動,以及Matlab打開驅動讀取FPGA算完的數據。根據異步串行通信的數據傳送格式,每一幀數據由起始位、數據位、奇偶校驗位和停止位組成,本文只選取了數據位,一共8位。通過串/并轉換接收數據,算完后存入RAM,然后調用數據,通過并/串轉換傳輸數據。

正弦波的輸出有10位,其中l位是符號位,另外9位是小數位,而系數左移5位后化成整數,在所得的整數中也有5位小數位,所以最終數據一共有19位,其中5位整數位,14位小數位。因為串口是8位一幀數據,為了運算簡便,選取了5位整數位,11位小數位,舍去最后3位小數,每個數分兩次傳輸。因為最后的數據分為實部和虛部,所以每個復數需要4幀數據傳輸。Matlab接收數據重新組合,還原成FPGA的計算結果。

評論