基于FPGA的無線信道模擬器設計

3 模擬器的性能測試與分析

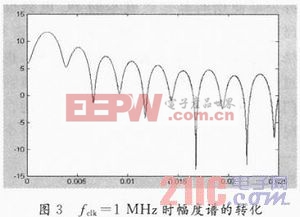

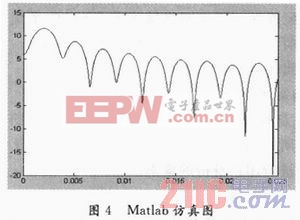

開發板的工作時鐘為100 MHz,DDS IP核延遲2個時鐘周期有輸出值,乘法器延遲1個時鐘周期有輸出值,所以系統總共有3個時鐘周期的延遲。串口傳輸數據比較慢,而且數據量太大容易出錯,所以將工作時鐘分別進行100倍分頻上傳衰落信道第一徑的25 000個數據進行觀察,工作時鐘變成1 MHz,將所得的幅度譜轉化成功率形式后如圖3所示,fclk=1 MHz的Matlab仿真如圖4所示。本文引用地址:http://cqxgywz.com/article/190237.htm

圖3和圖4中橫軸單位均為s,縱軸單位均為dB。通過比較圖3和圖4發現實際產生的結果與仿真結果大致相同,也因為系數的取整和最后上傳數據的截斷有少許誤差,基本滿足要求。

4 結語

本文采用Jakes改進模型,基于FPGA模擬了無線信道的傳輸特性,最終經過驗證基本滿足要求。為了簡化實現過程,將系數取整以及傳輸數據進行截斷,產生一些誤差,在這方面可以采用浮點數表示系數得到更精確的值。

評論