基于FPGA的可鍵盤控制計數電路的設計與實現

摘要:介紹一種基于FPGA(Field Programmable Gate Array)現場可編程門陣列的可鍵盤控制的計數,顯示電路的實現方法。應用VHDL語言(高速集成電路硬件描述語言)完成了3x4矩陣開關的掃描電路,可預置數的BCD碼計數電路及4位數碼管動態掃描電路的描述。通過原理圖輸入方式完成了系統功能的設計。電路結構簡單,便于擴展,可靠性高,且可移植性強,容易實現。該電路已成功應用于測試某脈沖電容質量試驗的控制電路中。

關鍵詞:FPGA;鍵盤掃描;計數;動態顯示

FPGA做為現代電子設計技術的核心器件,成為目前硬件設計研究的重點。在工業控制中,計數顯示基本電路在儀器儀表中得到了廣泛應用,而如何根據需要靈活的設置計數范圍,是一個較為復雜的問題。本文應用EDA技術通過對鍵盤的控制,實現了從0~9999范圍內預置數可變的計數顯示電路設計。與傳統的應用單片機控制鍵盤掃描的設計方法相比,具有集成度高,穩定度高,抗噪聲能力強,容錯率低等優點。

1 系統設計原理及電路圖

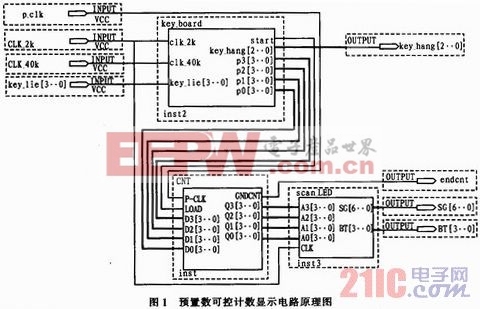

圖1為基于FPGA的預置數可控計數顯示頂層設計電路原理圖,共由3部分組成:鍵盤掃描控制電路key_board;BCD碼計數電路CNT;4位數碼管動態掃描顯示電路scan_LED。首先,由鍵盤掃描電路完成對鍵盤的掃描和鍵值的譯碼,當計數電路置數端LOAD為上升沿時,將鍵盤掃描電路讀取的數據經P3-P0并行置入到計數器中做為其計數范圍,計數器的輸出通過動態掃描譯碼模塊驅動4位數碼管顯示。

2 VHDL語言的實現

該設計采用層次化設計方法,首先采用VHDL語言完成了對各子模塊電路的描述,然后分別將其生成符號元件,通過原理圖編輯完成了系統的設計。

2.1 鍵盤掃描電路

2.1.1 行列式鍵盤工作原理

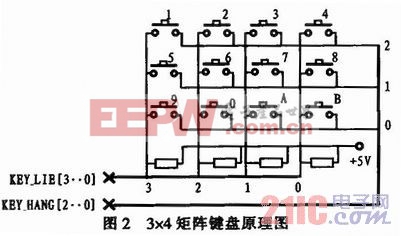

圖2為3x4行列式鍵盤原理圖,行線是KEY_HANG[2..0],列線是KEY_LIE[3..0],形成12個交叉點,每個交叉點連接一個按鍵。12個按鍵分別對應數字0~9和清零鍵A,確定鍵B。當沒有按鍵按下時,所有交叉點斷開,由于列線的上拉電阻作用,使其保持高電平。如果行線KEY_HANG[2..0]被設置為低電平,當有按鍵按下時,該鍵所在的行線和列線被按鍵短路,那么相應得列線就變為低電平。

評論