基于FPGA的時統模塊可靠性設計

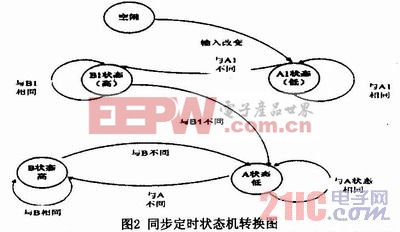

本板通過調線可以設置外部輸入有效電平(為高或為低),假設有效電平設置為高,其外部時統輸入的同步狀態機如圖2所示。本時統模塊在上電狀態初始化時便啟動全局計數器,當在A1狀態或在A狀態,以板載溫度補償晶振產生的精確的32MHz時鐘(誤差1Hz/32MHz)對輸入時統進行循環計數直到A1或A狀態改變,計數值為Count,在Count基礎上分別加上SET-Offset,SET+Offset便可以設置下一個時統時鐘周期上升沿調變在允許誤差范圍內的計數最小和最大允許值,其中SET為32MHz時鐘對一個完整時統周期的計數值,Offset為門限誤差。以移動標尺方式對下一次外時統輸入的沿調變設置了允許誤差范圍。如果在此限定的計數范圍內出現一次上升沿跳變,說明此時有外時統輸入,該時統信號是有效的,并依據此上升沿作為同步,向外提供各種同步時統信號,同步誤差為一個計數周期,即20ns。假如在此限定的計數范圍內沒有出現上升沿跳變,則產生一個錯誤標志位。說明沒有外時統信號輸入,或者外部輸入時統信號無效,此時經由板載溫補晶振產生的32MHz分頻后,產生所需要的各種時統信號,對外轉發,做到自守時功能。一旦有有效的外部時統輸入,便可進入同步狀態。若沒有有效時統輸入,立即轉入自守時狀態。本文引用地址:http://cqxgywz.com/article/191093.htm

2 高速電路EMC設計

目前該時統模塊主要運用于CPCI系統,基于PCIExpress接口的電路屬于高速電路,硬件設計中的關鍵要點是高速電路設計,進行高速電路的PCB設計,首先要充分考慮電磁兼容(EMC)。因為數字電路板形成的磁場天線和電場天線往往是整機設備最大的干擾源,其EMC性能好壞直接影響到設備的功能運行和認證測試。同時,設計初期考慮電路板的EMC問題,可以降低成本,提高產品合格率,縮短開發周期,提高系統的抗干擾能力和可靠性。

數字電路板中因為分布參數引起共電源阻抗耦合和共地阻抗耦合的共模輻射是最多的,而回流面積過大、回流集中問題往往是起因;同時注意密集的過孔、通孔、過大的安全間距、電地層的分割會破壞參考面的完整性,達不到EMC預想效果。

時統接收處理模塊數字電路板布局時,時鐘發生/緩沖分配器首先放置,并且要滿足其間隔距離要求。時鐘信號先走線,可以通過串接阻尼電阻或適當的慮波,增大高速信號的上沿時間和下沿時間,減小信號產生的電磁輻射強度和諧波數量,或者采用隔離技術如光隔、變壓器隔離等,同樣能過濾高頻噪聲。在可能的情況下,高速的時鐘和信號線最好能跟地走,以達到回流面積最小的效果,也能解耦電容大小配備適當,并盡量靠近器件的電地管腳附近,不但能減小信號環流面積,而且能減小電源層耦合噪聲的可能性,從而減小共電源阻抗耦合的共模輻射;鋪銅要寬且不能留孤島,銅皮上多打過孔并和地良好端接;信號線不懸空并實現良好端接;器件無用管腳和地良好端接,防止形成電場天線造成共模輻射;另外,3W規則和20H規則的執行、器件的浪涌保護等也可以增強數字電路板的EMC。

3 PCB仿真技術

通過進行PCB仿真,能啟發新的思想或產生新的策略,還能暴露出原系統中隱藏著的一些問題,以便及時解決。高速串行電路設計中一個重要的技術難點就是如何保證信號的完整性,在進行PCB設計過程中,有針對性地對模塊進行信號完整性分析,對提高系統的抗干擾能力、可靠性有很大的幫助。在本設計中采用的仿真工具是Mentor公司Hyperlynx GHz,Hspice仿真模型由器件的生產廠家提供。

仿真的過程主要包括前仿真和后仿真,以下敘述兩種仿真的具體內容。

3.1 前仿真的實現

前仿真是在進行電路布線之前進行的仿真,也即是功能仿真。前仿真的主要目的有兩個:驗證原理設計的正確性,為電路布線提供設計參數。所以在這個仿真過程中只需要進行一些基本參數的設置,通過調整參數對比仿真的結果,在前仿真時不需要將PCB的全部信息導入。

評論