基于FPGA的時統模塊可靠性設計

3.1.1 阻抗控制

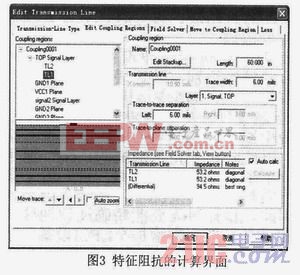

PCI Express規范對信號線的特征阻抗要求為:差分阻抗100 Ω,單端阻抗50 Ω,特征阻抗的誤差范圍為±10%。特征阻抗主要由線寬、線間距、銅皮厚度、介質層厚度、介質材料等因素決定。特征阻抗的計算界面如圖3所示,經計算,特征阻抗為94.5Ω,滿足要求。本文引用地址:http://cqxgywz.com/article/191093.htm

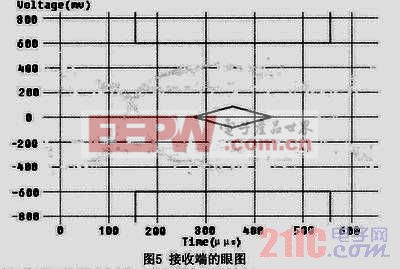

在高頻電路中,損耗是一個需要重點考慮的因素。在設計中需要采取控制線長、選擇介質等手段加以控制。根據在模塊上可能出現的最壞情況設置參數:表層走線寬度0.1778mm,走線間距0.1524mm,走線厚度0.1016mm,走線長度為762mm的情況下得到結果如圖4所示,進行仿真得到驅動端的眼圖符合要求。

3.2 后仿真的實現

后仿真主要是在PCB繪制完成后,在前仿真的基礎上將PCB相關的數據導入后再進行的仿真。在將PCB參數導入后進行仿真,結果如圖5所示。信號幅度滿足要求,在接收器可以識別的范圍之內。

根據仿真的結果,得到如下結論:

(1)制板時,要求PCB廠家將差分阻抗控制在100 Ω;

(2)PCI Express總線要按照差分線方式走線,差分對間距保持一致;

(3)PCI Express總線差分對之間的間距保持在0.762mm以上(有空間盡量大);并且和其它類型信號線的間距盡量保持在0.762mm以上(有空間盡量大)。

(4)時鐘線一定要走成差分線,保持與其它信號線間距大于0.762mm。

4 結束語

本文詳細介紹了作戰系統時間統一同步的可靠性設計,從EMC設計、高速電路PCB設計、FPGA邏輯編程設計等幾個方面介紹了時統接收處理模塊的抗干擾設計及其實現方法,并用仿真技術進行仿真,從而將時統系統可能受到的干擾減到最低,提高了整個作戰系統的可靠性。文中的時統模塊已經應用于實際的作戰系統中,效果良好。

評論