基于FPGA的LCoS驅動和圖像處理系統設計

摘要:針對分辨率為1 024×768的LCoS屏編寫了Verilog HDL驅動代碼,在quartusⅡ9.1平臺上綜合編譯,并在Altera的FPGA芯片EP3C5E14 4C8上進行了功能驗證和實際輸出信號測量。采用異步FIFO結構解決了跨異步時鐘域的數據傳輸問題。嵌入FFT IP核后,可進一步對圖像進行基于FFT的變換處理,分析圖像的頻譜。為計算全息3D圖像處理及顯示提供了硬件平臺。

關鍵詞:Verilog HDL;LCoS;異步FIFO;FFT

0 引言

基于空間光調制器的計算全息三維顯示技術,目前常采用透射式LCD和反射式LCoS作為空間光調制器,以改變光經過空間光調制器(SLM)后的空間相位和振幅分布,達到對光信息的調制。傳統的基于透射式LCD空間光調制器的計算全息三維顯示系統,其成像光路復雜,而且必須依賴計算機進行數據發生、采集以及處理,這就限制了系統應用的靈活性,不便于推廣。

相較于透射式LCD,LCoS具有光利用率高、體積小、開口率高、器件尺寸小等特點,可以很容易地實現高分辨率和微顯示投影。采用彩色LCoS屏顯示基于RGB的彩色圖像,經過光學成像系統投影到接收屏上,實現計算全息圖像的三維顯示。

基于FPGA的顯示系統有以下優勢:第一,LCoS尺寸小,便于實現微投影,利用可靈活編程的FPGA器件作為驅動控制器,這樣就可以將其做成像普通投影儀一樣的微型投影設備,使計算全息三維顯示擺脫了計算機和復雜光路的束縛,具有了更高的靈活性,為其走出實驗室提供了條件。第二,因為在傳統空間光調制器上得到的圖像里含有物波和參考光的復共軛像,形成了噪聲,在FPGA上可以實現圖像濾波去噪,使得到的圖像更清晰。第三,FPGA是基于可編程邏輯單元的器件,當經過綜合、布局布線、時鐘約束的代碼燒錄到FPGA器件后,FPGA就將算法代碼硬件化了,可以作為專用芯片工作,其內部信號延時完全是硬件級傳輸延時。在處理數據搬移和復雜的數學運算以及一些循環操作時,例如圖像的FFT變換,FPGA硬件運算要比軟件運算快得多,即利用FPGA器件實現對軟件算法的硬件加速。

基于以上原因,本文設計了基于FPGA的LCoS驅動代碼及圖像的FFT變換系統,為計算全息三維顯示圖像處理和顯示提供了硬件平臺。

1 系統設計

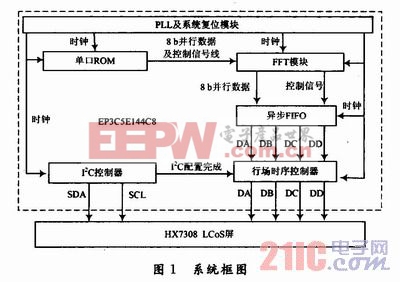

1.1 系統模塊框圖:

該系統采用cycloneⅢEP3C5E144C8,該芯片有5 136個LE,95個用戶I/O,2個PLL,以及46個嵌入式乘法器和423 936 b的內部邏輯寄存器。以它豐富的資源,完全可以作為LCoS的驅動控制器件。顯示屏采用Himax的反射式LCoS屏HX7308,其分辨率為1 024×768,可以支持256級灰度顯示,具有內置的行場驅動電路,在外部輸入時鐘的上升沿和下降沿分別接收8b×4dots圖像數據,這保證了場頻可高達360 Hz。

系統的整體框圖如圖1所示。

評論