基于FPGA 的衛星便攜站的同步數字復接器的設計

1.2 設計方案

1.2.1 幀結構

該單元不要求與其他復分接設備互聯互通,所以采用自定義的幀結構。幀頭采用集中幀碼,幀頭固定為12 bits。幀結構如表1 所示。

根據表1 可以計算出每幀的幀長L 為7 680 bit,線路速率R 為768 kbps 時,幀周期T 為:

幀頻F s 為:

表1 幀結構

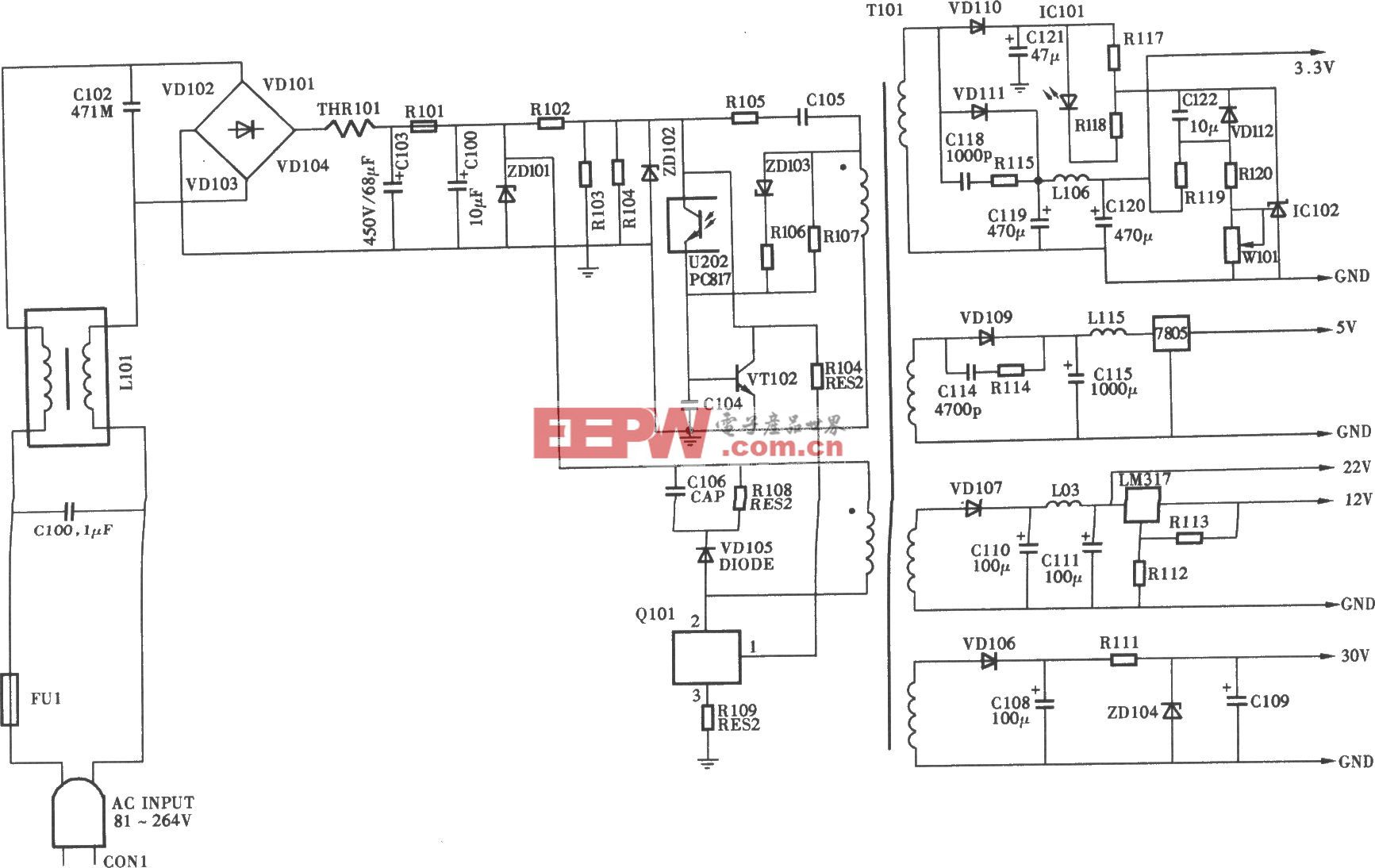

1. 2. 2 復接器

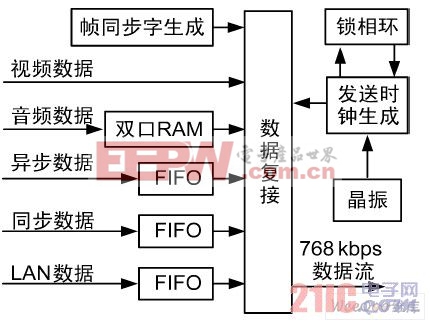

復接器部分負責將各支路信息數據和幀頭合成一路數據流。它由時鐘發送電路、數據接收存貯器、數據緩沖單元和數據復接電路組成。時鐘發送電路產生復接各支路信息數據所需的時隙,時鐘通過使用內部時鐘源或由接收時鐘鎖相得到; 數據接收存貯器為一雙口RAM,用來接收數字音頻數據; 數據緩沖單元用來把同步數據等數據的相位調整到滿足可以進行復接的相位; 數據復接電路將上述數據合成一路線路數據; 復接器的組成框圖如圖2 所示。

圖2 復接器組成框圖

評論