基于FPGA的高速同步HDLC通信控制器設計

而多項式乘除法運算過程與普通代數多項式的乘除法相同。多項式的加減法運算以2為模,加減時不進位或錯位,和邏輯異或運算一致,即加法和減法等價。則對上述例舉的數據的CRC計算過程如圖6所示。本文引用地址:http://cqxgywz.com/article/191467.htm

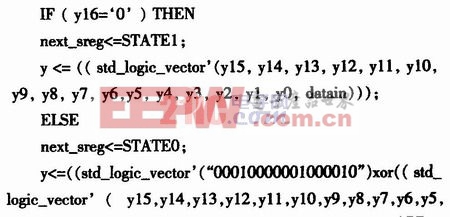

模擬上述計算CRC校驗值的方法,不難想到可用狀態機實現,設置一個17位的矢量,檢驗最高位是否為零。如果為零,則跳轉到狀態1,即所有位左移,最低位補1位數據;如果不為零,則跳轉到狀態0,最低位補1位數據,與“00010000001000010”異或,(以CRC-CCITT為例,由于y16與‘1’異或必為‘0’,datain與‘0’異或還為datain),這種思路的VHDL代碼如下:

圖7為該VHDL代碼的仿真波形,可看到該方法模擬對2取模整除的一步步計算。

該方法思想簡單,是對2取模整除方法的模擬,直觀,易于理解,由于是串行輸入,不受需要CRC計算的數據位數限制。由于HDLC通信協議的最大優點是對要傳輸的信息文電比特結構無任何限制,也就是說,信息文電可以是任意的比特串,不會影響鏈路的監控操作。因此,這里給出的CRC串行算法符合HDLC傳輸文電比特結構任意的特點。

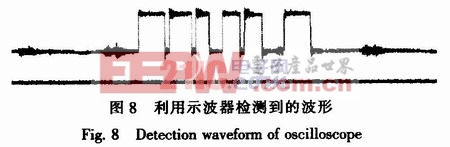

3 程序加載驗證

經過邏輯綜合和時序仿真后,利用ISE 9.1i集成開發軟件將程序燒入FPGA,利用示波器觀測FPGA按HDLC通信協議標準發出的信號。如要發送的“有效信號”(不含幀頭幀尾,未進行CRC校驗及‘O’比特插入之前的原始數據)為“llll llll”,則經過FPGA處理后應發出的數據為“0111 1110 1111 1011 1000 1111 0111 1000 0011 1111 0”,利用示波器檢測到的信號波形如圖8所示。

由圖8可知,對數據進行CRC校驗,‘0’比特插入及加幀頭幀尾操作,發送數據正確,符合HDLC通信協議標準。

4 結束語

由于HDLC通信協議具有透明傳輸、可靠性高等優點,在數據鏈路層應用廣泛,而FPGA更具有靈活、高性能、低成本、平臺化、可定制等優點,具有系統級能的復雜可編程邏輯器件和現場可編程門陣列實現可編程片上系統也成為今后的發展方向。本文提出的基于FPGA實現HDL-C/SDLC協議方法采用ISE 9.1i編譯、綜合、仿真、布線、燒寫,ISE軟件支持器件多,功能強大,操作更方便,因此,該實現方法具有很強的實用性,另外,程序加載入FPGA后發送數據正確,說明該實現方法實用、有效。

評論