基于CPLD的數字電壓表設計

1 方案論證與比較

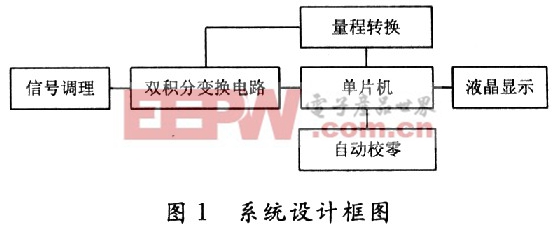

雙積分A/D是對輸入取樣電壓和基準電壓進行兩次積分,以獲得與取樣電壓平均值成正比的時間間隔,同時在此時間間隔內,用計數器對CP記數,計數器的輸出結果就是對應的數字量。雙積分A/D有精度高,抗干擾能力強和穩定性好的優點,但轉換速度較低,因而適用于數字直流電壓表等精度較高而轉換速度要求不高的儀器。設計的系統框圖如圖1所示。為實現該系統功能,可采用以下兩種方案。

1.1 方案一

用J-K觸發器構成n位二進制異步加法計數器,并采用下降沿觸發器FF。但因J-K觸發器數目與顯示精度有關,若顯示精度較高,則所需觸發器數目較多,需占大量空間,且易受干擾。若2 V檔的最小分辨率為0.1 mV,則有2/(2n-1)=O.1 mV,n≥15,這里取n=16,如圖2所示。

1.2 方案二

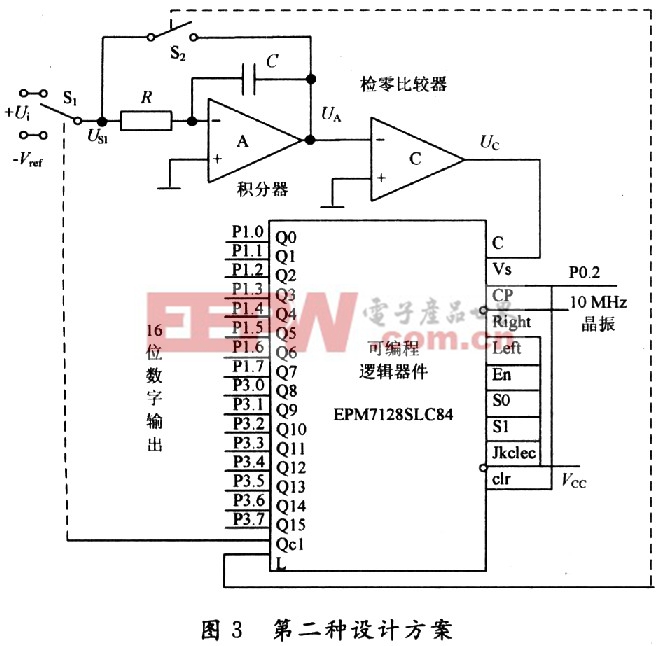

采用EDA可編程邏輯器件把16位J-K觸發器組成的計數器和控制電路集成到系統內部,不僅可以消除外界干擾,減小測量誤差,且大大節省空間,提高系統的響應速度。CPLD使用方便、快捷,性價比很高,如圖3所示。

對比兩種方案的性能,本設計選用方案二。

2 系統設計

2.1 硬件部分

2.1.1 濾波電路

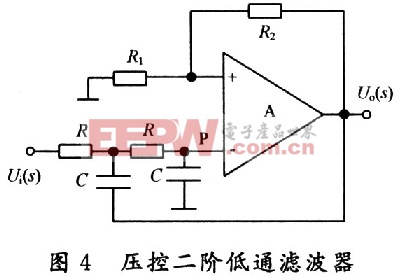

濾波電路采用壓控二階低通濾波器,如圖4所示。運放采用低溫漂高精度運放OP07,取R1=R2=R=1.592 kΩ,C1=C2=10μF,則f0=10 Hz。

評論