基于FPGA的任意波形發生器設計與實現

(3)數據存儲芯片SRAM。考慮到成本的因素,本系統采用ISSI公司的IS6lLV25616-10T。

(4)D/A轉換芯片。本設計使用的是AD9726,該芯片控制信號簡單,D/A轉換速度快,因此將系統的硬件設計大為簡化,也減輕了系統軟件設計的工作量。

(5)FPGA控制芯片。本設計使用的是Altera公司的Cyclone II系列型號為EP2C20F484的FPGA。EP2C20F484以90nm工藝技術為基礎,提供了18,752個邏輯單元(LE),并具有一整套最佳的功能,包括嵌入式18位×18位乘法器、專用外部存儲器接口電路、4kbit嵌入式存儲器塊、鎖相環(PLL)和高速差分I/O能力等。本文引用地址:http://cqxgywz.com/article/191658.htm

2 系統功能及硬件實現

2.1 USB傳輸模塊

CY7C68013有2種接口方式:Slave FIFOs和可編程接口GPIF。當FPGA與其相連時,只需要利用CY7C68013作為一個USB2.0數據通道來實現與主機的高速通信。

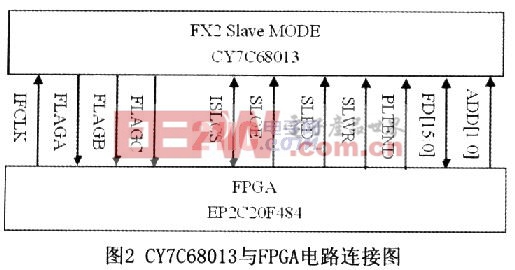

Slave FIFOs方式是從機方式,外部控制器可像普通FIFO一樣對CY7C68013的多層緩沖FIFO進行讀寫。CY7C68013的Slave FIFOs工作方式可設為同步或異步;工作時鐘可選為內部產生或外部輸入,其它控制信號也可靈活地設置為高有效或低有效。電路連接圖如圖2所示。

IFCLK是同步時鐘信號,FLAGA、FLAGB和FLAGC是CY7C68013內部FIFO的狀態標志,EP2C20F484通過通用I/O口獲得CY7C68013內部FIFO的空、半滿(由用戶設定半滿閾值)和滿這三個狀態信號,ISLCS、SLOE、SLRD、SLWR對CY7C680l3進行讀寫操作控制,FD[15:0]是數據線,ADD[1:0]是選擇4個FIFO的地址線。其工作過程為:PC機通過USB向FPGAP發送波形數據時,USB通過請求方式通知FPGA讀取波形數據,FPGA首先查看空、半滿和滿這三個狀態信號,選擇一個FIFO,然后控制USB接收適當大小的數據,以保證數據不會溢出,并存入SRAM中。

2.2 DAC功能模塊

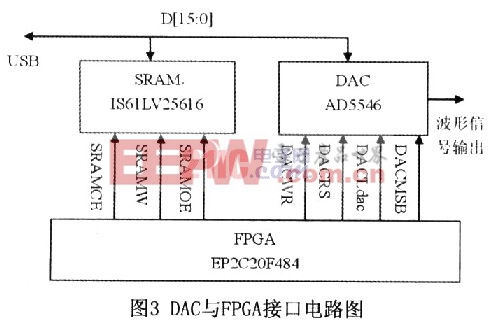

從總體工作過程分析可知,從USB接口下載的波形數據存儲在SRAM中,SRAM循環輸出數據到DAC芯片,根據DDS原理產生模擬波形。具體電路如圖3所示。

IS6lLV25616是256k×16高速CMOS工藝3.3V單電源供電的靜態隨機存儲器(SRAM),在FPGA控制下存儲從USB下載的數據,并將數據循環輸出到DAC芯片。AD9726是一款16位高性能LVDS DAC,具有出色的噪聲與雜散性能以及真16位直流線性度。它采用CMOS工藝制造,并利用專有開關技術來增強動態性能。該器件具有較寬的滿量程電流調節范圍(2mA至20mA),能夠以較低功耗水平工作。其電流輸出配置簡便,可以用于各種單端或差分電路拓撲結構。

評論