基于FPGA的任意波形發生器設計與實現

3 系統軟件設計與實現

3.1 固件程序設計

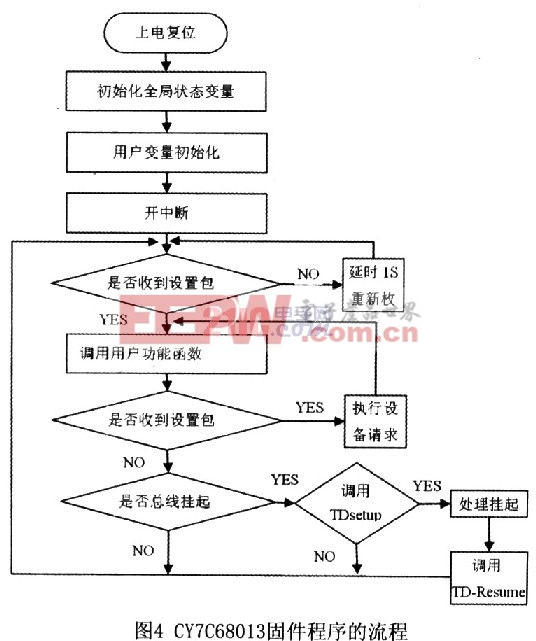

CY7C68013內嵌有8051微處理器,用于控制芯片的工作狀態設置,寫入微處理器的程序文件稱為固件程序(Firmware),為了便于維護和移植,一般采用單片機的C語言編寫。主要有以下幾種功能:a.初始化工作,包括設置一些特殊功能寄存器的初值以實現所需的設備屬性或者功能,例如開中斷、使能端點、配置端口等。b.輔助硬件完成設備的重新列舉過程,包括模擬設備的斷開與重新連接,對接收到的設置包進行分析判斷,從而對主機的設備請求作出適當的響應,完成主機對設備的配置任務。c.對中斷的處理。d.數據的接收和發送。e.外圍電路的控制。固件程序的流程如圖4所示。

3.2 FPGA程序設計

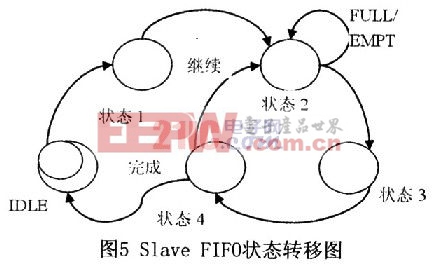

在本系統中FPGA作為主控制器,提供USB控制、DA控制、SRAM控制、I2C控制及全局時鐘控制等功能模塊。這里重點介紹USB接口控制模塊。固化程序將CY7C68013A設置為Slave FIFO工作模式,需要FPGA提供FIFO端口的讀寫操作控制時序。CY7C68013A為每個端口提供了”空”標志、”滿”標志和”可編程級”標志。FPGA檢測這些信號,用于控制讀寫的過程,FPGA再完成這些端口FIFO的操作時序控制。USB控制器的狀態轉移如圖5所示,控制器工作在五個狀態中,上電復位后工作在IDLE狀態,當讀/寫事件發生時進入狀態1;在狀態1中根據讀/寫事件使能FIFOADR[1:0]指向相應FIFO并進入狀態2;在狀態2,如果FIFO空/滿,在當前狀態等待,否則進入狀態3;在狀態3中,驅動數據總線,完成讀/寫操作,進入狀態4;在狀態4中,如需傳輸更多數據,進入狀態2,否則進入狀態IDLE。本系統采用Verilog HDL硬件描述語言實現了FIFO的讀寫時序,并在ALTERA公司提供的QuartusII8.0開發工具中綜合編譯并映射到FPGA中運行。

4 結果及分析

在設計結果中,最后的波形圖是使用泰克公司的TDSl012型示波器得到的。經過實際的測試,該信號發生器產生的波形精度高、失真小,完全滿足設計的要求。圖6是產生的正弦波、鋸齒波的波形結果。

評論