基于FPGA的偽隨機序列發生器設計

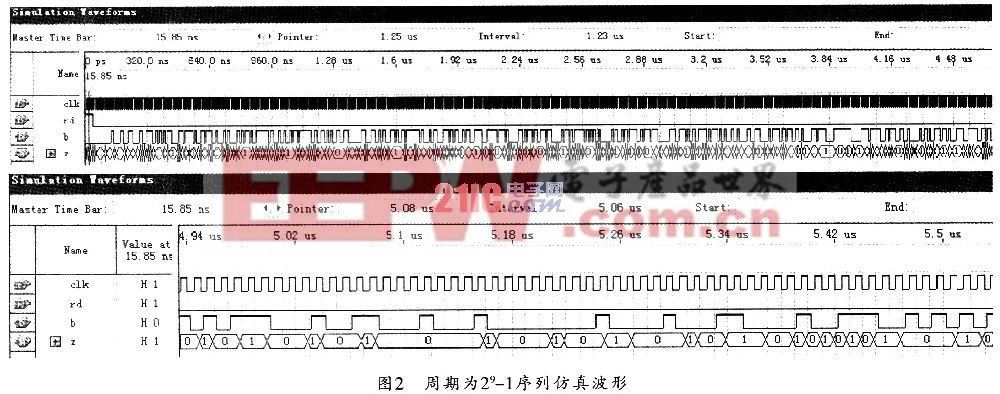

圖2所示是該序列在QuaitusⅡ開發平臺中的仿真波形。

其中,斜體0、1代碼表示序列又一周期的開始,周而復始。

1.2序列偽隨機性分析

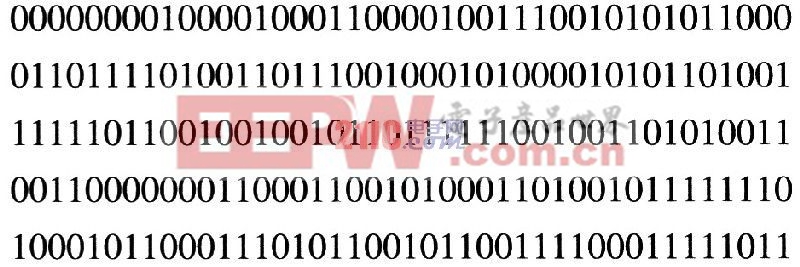

對本原多項式是的m序列偽隨機性進行分析時,主要是分析其平衡性和游程特性。首先是平衡性。通常在一個周期中,m序列的l出現的次數為2n-1次;0出現的次數2n-1-1次。其次是游程特性。即對于Ok≤n-2,其長度為k的0游程出現2n-k-2次;長度為k的l游程也出現2n-k-2次;長度為n-1的0游程出現1次;長度為n的l游程出現1次。以上就是其中出現的全部游程。

平衡性和游程特性分析表明該序列符合m序列的統計特性。

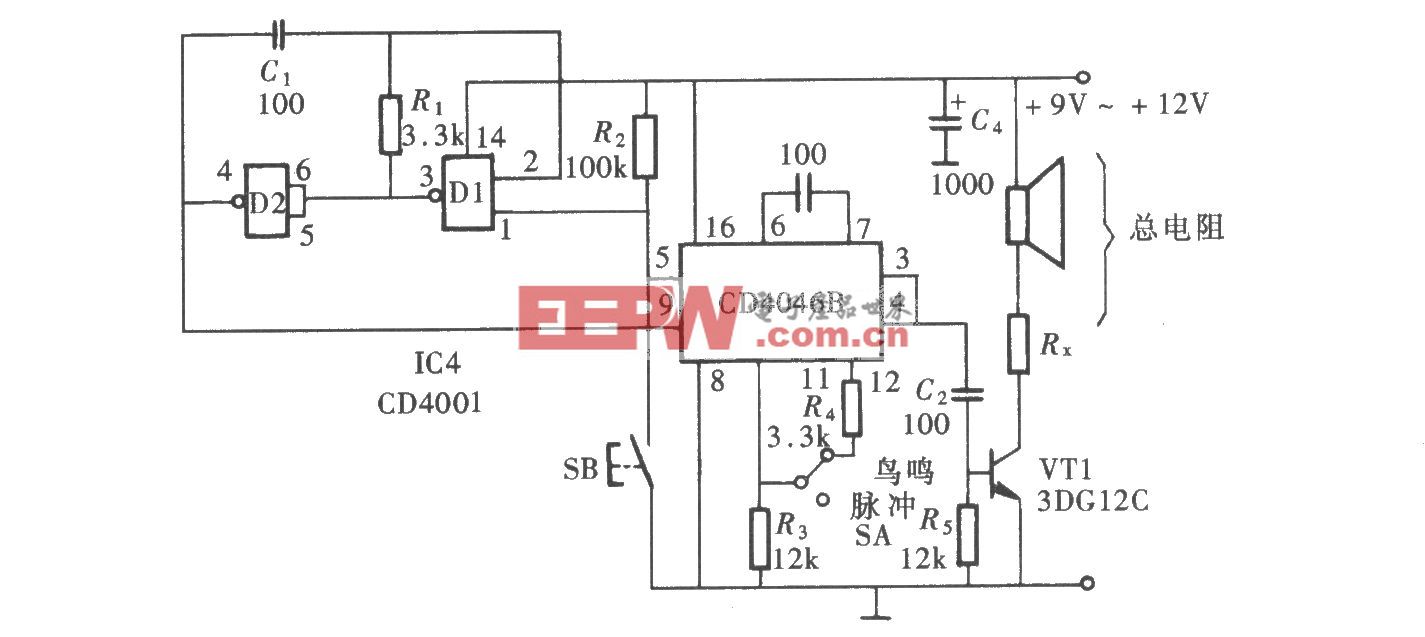

2 非線性m子序列實現

m子序列是與m序列具有同周期、相同平衡性和不同局部游程的序列,m子序列移位寄存器的反饋多項式與m序列移位寄存器的反饋多項式的關系,可以根據m子序列的構造思想來計算,其中交換一對共軛狀態的后繼意味著反饋函數f(x)在共軛狀態處取補,其中s=(s0s1…sn-1),,即f(x)’=f(x)+1。其它狀態處反饋函數不變,即f(x)’=f(x)+0。因此,可由布爾函數理論推知:

評論