基于FPGA的可層疊組合式SoC原型系統設計

垂直層疊模式需要占用原型模塊的全部4個連接器,不能再支持其他功能擴展模塊,如高速AD/DA模塊、視頻采集模塊等,因此適合外圍接口較少的SoC驗證。如果外圍接口應用豐富,如多媒體SoC驗證,就需要采用平鋪式層疊模式。

2.2 平鋪層疊模式

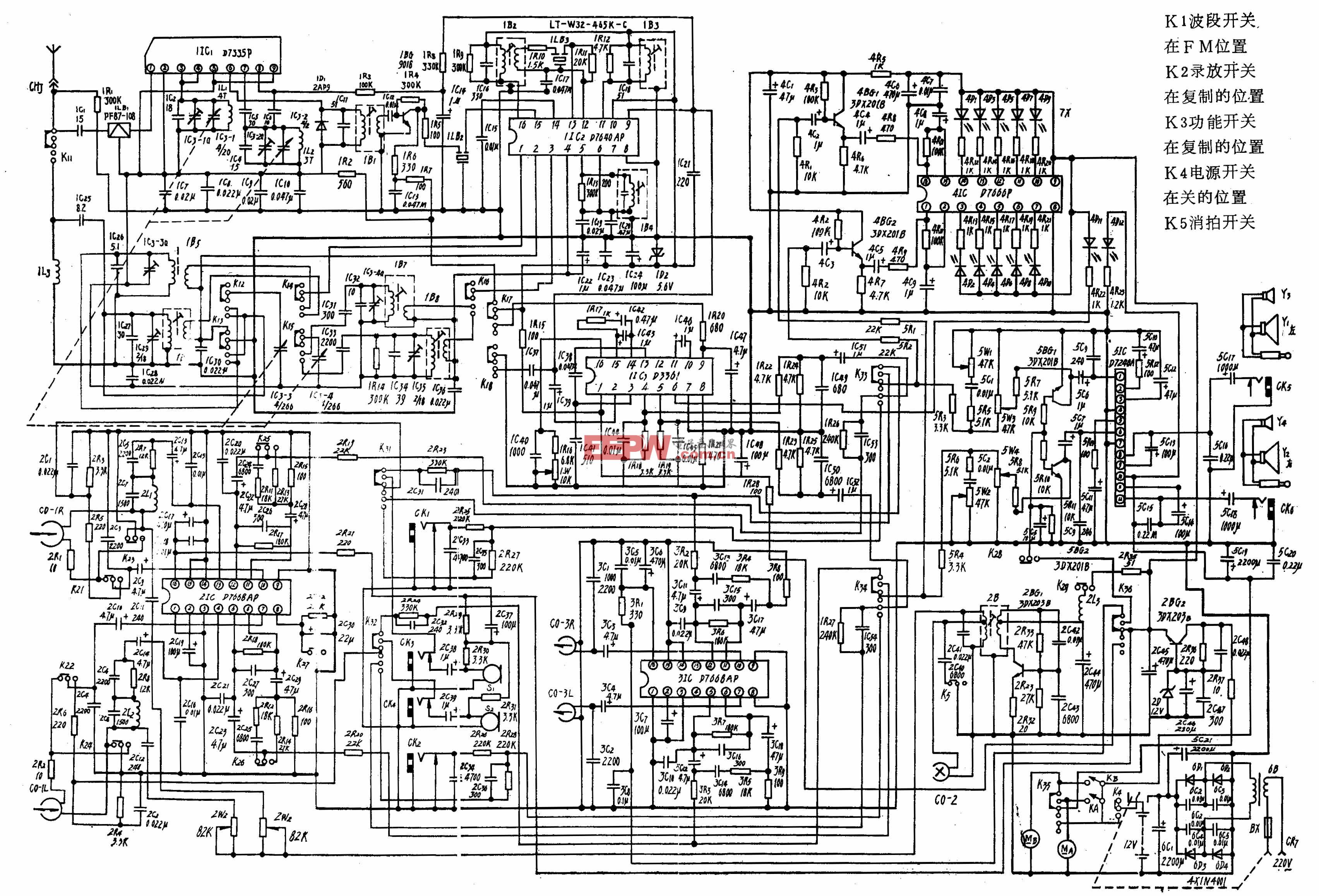

平鋪層疊模式是將一個SoC驗證模塊作為系統主控模塊位于上方,其他SoC驗證模塊作為輔助模塊平鋪于下方。每個輔助模塊通過一個連接器和主控模塊通信,共享120個I/O管腳。這種模式支持5個原型模塊層疊。輔助模塊另外的3個連接器可以用來擴展多種類型的接口板,可以實現非常豐富的接口類型。

以5個原型模塊平鋪層疊為例,其JTAG環路示意圖如圖9所示。其中原型模塊1為主控模塊,其他為輔助模塊。

3 原型驗證實例

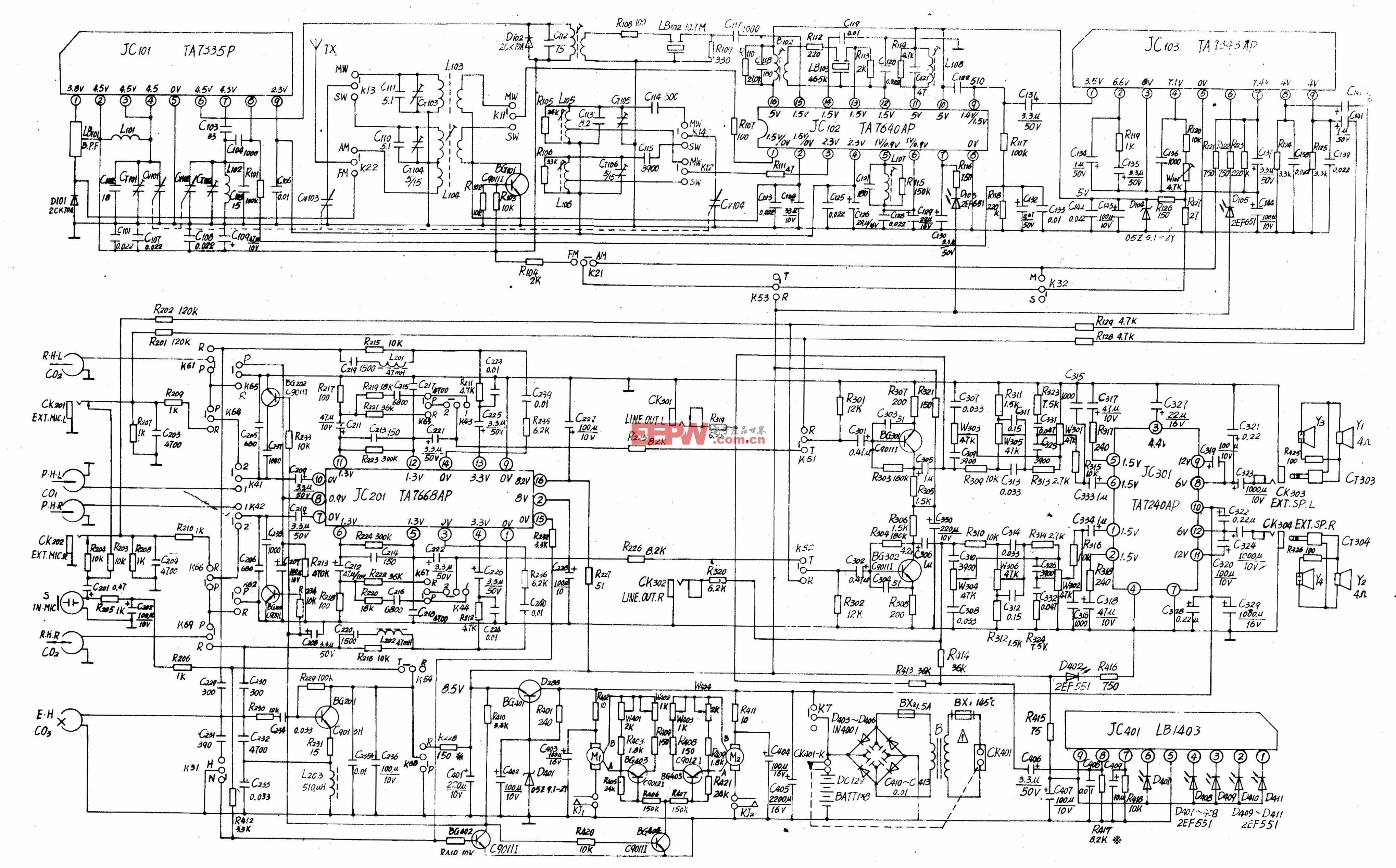

DTMB是具有自主知識產權的中國數字電視地面廣播傳輸系統標準,采用了多項利于提高系統性能的關鍵技術,適用于固定和移動兩種數字電視接收模式,并支持多業務的混合模式。BHDTMBT1006是北航通信測控技術研究所自主研發的地面數字電視多媒體廣播基帶調制芯片,其原型驗證就是在本文設計的SoC驗證系統上完成的。

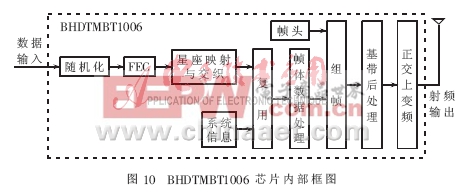

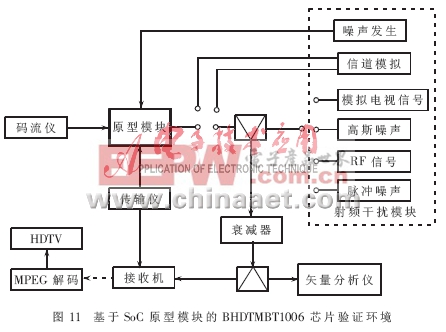

BHDTMBT1006芯片的內部框圖如圖10所示。在SoC原型模塊上,驗證程序以芯片的實際工作頻率來運行“實速”驗證,驗證環境如圖11所示。

在SoC原型模塊上主要測試了以下8種模式,包括:

(1)FEC 0.4,長交織,4QAM,PN420,C=3780,無導頻

(2)FEC 0.4,長交織,4QAM,PN420,C=1,無導頻

(3)FEC 0.6,長交織,64QAM,PN420,C=3780,無導頻

(4)FEC 0.6,長交織,64QAM,PN420,C=1,無導頻

(5)FEC 0.8,長交織,4QAM-NR,PN595,C=3780,有導頻

(6)FEC 0.8,長交織,4QAM-NR,PN595,C=1,有導頻

(7)FEC 0.8,長交織,16QAM,PN595,C=3780,有導頻

(8)FEC 0.8,長交織,16QAM,PN595,C=1,有導頻

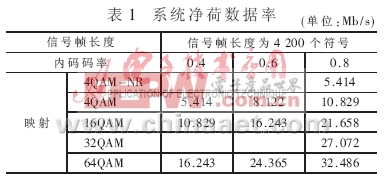

在信號幀長度為4 200個符號情況下,系統有效凈荷數據率測試結果如表1所示。

經過SoC原型模塊驗證后,BHDTMBT1006芯片已經成功流片。封裝后樣片的測試結果與SoC原型測試參數一致。

本文提出了一種基于FPGA的可層疊組合式SoC原型驗證系統,并且給出了實現方法。由于采用了創新性的互補型連接器和JTAG控制器,實現了多個原型模塊的拼接組合,可以適用于不同領域、不同規模的SoC原型驗證。結合了軟件硬件協同設計流程,大大降低了SoC驗證的復雜度,提高了SoC系統驗證的效率。

參考文獻

[1] 豐玉田,付宇卓,趙峰.大規模SoC設計中的高效FPGA驗證技術的研究與實現[J].電子技術應用,2006(2).

[2] 夏飛,劉光明.基于FPGA組的ASIC驗證原型系統和邏輯分割算法的研究與實現[J].計算機工程與科學,2006(9).

[3] LIN Yi Li,YOUNG Chung Ping,Su.A.W.Y.Versatile PC/FPGA-based verification/fast prototyping platform with multimedia applications.Instrumentation and measurement,IEEE Transactions on,Volume 56,Issue 6,2007(12):2425-2434.

[4] GSCHWIND M.FPGA prototyping of a RISC processor core for embedded applications.IEEE transactions on very largescale integration(VLSI) systems,2001,9(2).

[5] Altera Inc..Stratix II Datasheet,2008.

評論