FIR帶通濾波器的FPGA實現

本文引用地址:http://cqxgywz.com/article/191893.htm

2 Simulink的模型仿真

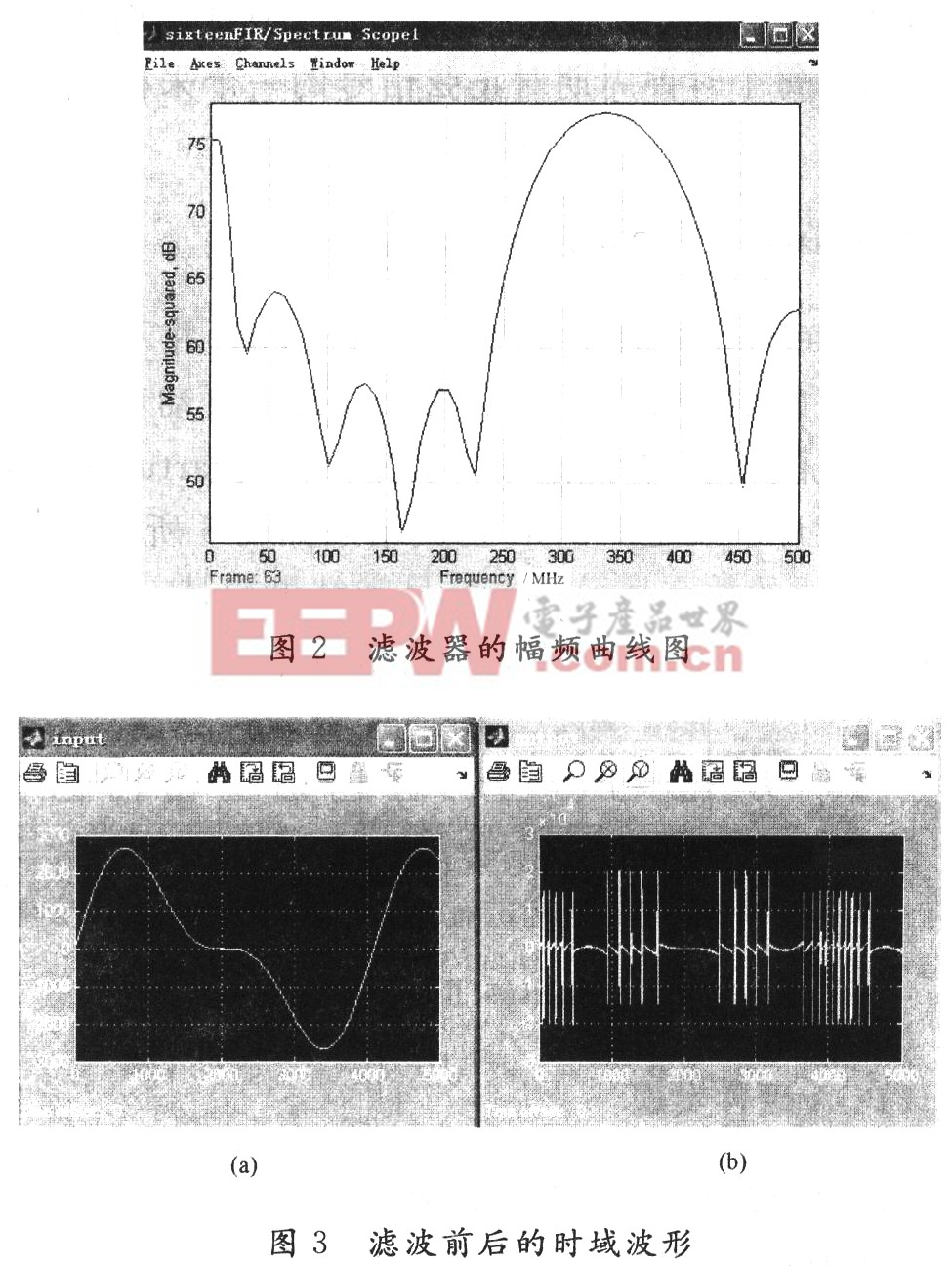

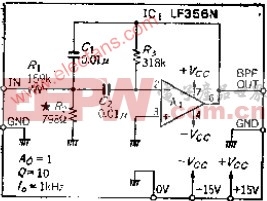

在Simulink環境下設計仿真時間等參數,運行仿真得到濾波輸出的幅頻相應圖和時域圖如圖2,圖3所示。

圖2中縱橫坐標分別代表了幅值和頻率值顯示,Magnitude,Frequency單位分別是dB(幅值單位也稱衰減倍數)和MHz(橫坐標每格單位相比kHz被放大104便于觀察)。縱橫軸每格量為5 dB和50 MHz。從該頻譜圖中可看出,濾波后通帶內幅頻曲線相對平緩,帶外衰減較大,由濾波前的連續幅頻變成了選擇通過的單一幅頻曲線,起到了過濾帶外頻譜的作用。

該圖坐標軸的縱橫軸分別代表了幅度值和時間軸。單位分別為十進制數和s。圖3(a)是兩正弦信號經平行加法器合成的波形圖3(b)濾波后的波形。可見高頻信號衰減很大起到了過濾帶外時間離散信號的作用。綜上該帶通濾波器在頻域和時域都實現了相應的濾波功能,至此完成了模型仿真。

評論