FIR帶通濾波器的FPGA實現

本文引用地址:http://cqxgywz.com/article/191893.htm

3 在ModeISim中實現RTL級仿真

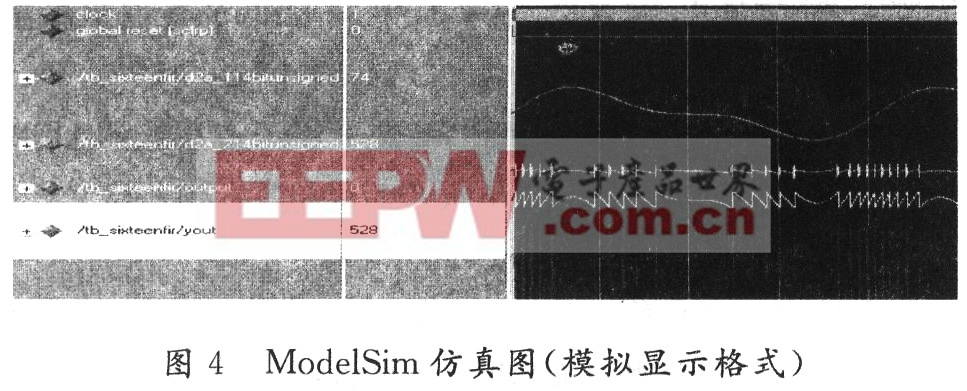

Simulink中僅實現了算法級的仿真,而ModelSim需要對生成的VHDL代碼進行功能仿真即RTL級仿真。如圖4的波形。

圖4定性表述了6個信號波形。clock為時鐘周期,第二個信號是全局復位。重點觀察第三、六個信號,分別是輸入信號(加了數/模轉換的)的模擬顯示和經濾波后輸出信號的模擬顯示。這和Simulink中仿真結果是一致的。第四個信號是濾波后(加數/模轉換)的信號,第五個是最后一個4階濾波子系統的輸出。同樣可設置ModelSim對應的數字顯示,每個時鐘周期對應的數值即為每個時鐘周期對正弦信號的一個采樣點計算一次的值。

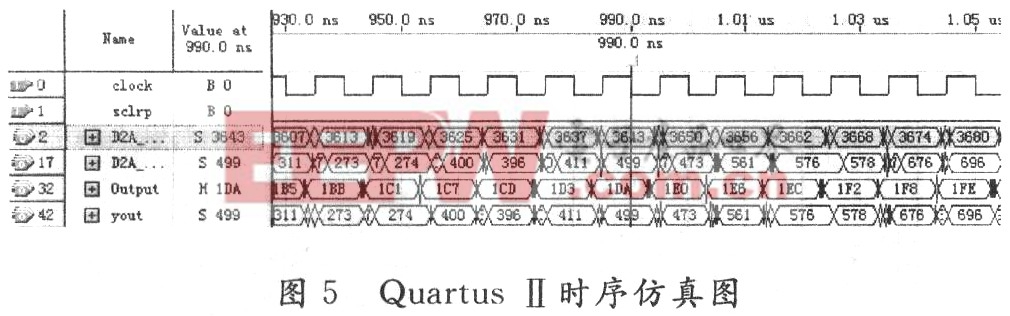

4 在QuartusⅡ中實現時序仿真

ModelSim中也僅實現RTL級仿真,并不能精確反應電路的全部硬件特性。Altera提供自動和手動兩種綜合適配流程,在此選用自動流程在QuartusⅡ中進行硬件設計。設定990 ns仿真結果如圖5所示與圖3ModelSim的數字顯示對應信號和結果均是一致的,只是QuartusⅡ的時序仿真更為精確。

5 FPGA硬件實現

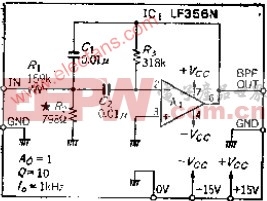

系統仿真通過后,需轉到硬件上加以實現,這是整個DSP Builder設計中最為關鍵的一步。QuartusⅡ仿真中生成了.sof編程文件,用于FPGA編程配置,完成了對開發板StratixⅡEP2S180特定芯片的編譯和管腳的分配。將.sof文件下載到開發板中,編程模式為USB Blaster相應模式為JTAG,用示波器檢測D/A輸出,可觀察到實測的輸入/輸出波形與仿真結果均對應一致。至此完成了該濾波器完整的FPGA開發設計,并驗證了該濾波器達到預期設計要求。

6 結 語

這里介紹在Altera DSPBuilder。環境下基于模型化設計FIR數字帶通濾波器的方法,通過模塊化的方法實現了向VHDL硬件描述語言代碼的自動轉換、RTL級功能仿真、綜合編譯適配和布局布線、時序實時仿真直至對目標器件的編程配置和硬件實現。驗證了濾波器滿足預期設計要求。創新點在于便捷地設計模塊或修改基本參數,完成其他DSP系統設計。綜上采用DSP Builder作FPGA設計,可以更快速、可靠、有效地實現系統功能。體現了FPGA技術的便捷和發展。

評論