基于FPGA的兩路視頻同步播放系統的設計

2.2.3重疊區域采樣電路模塊設計輸入視頻信號重疊區域采樣窗模塊是由兩塊uPD42280芯片串聯構成。通過 FPGA對uPD42280芯片發出控制信號,達到對指定像素區域進行采樣的目的。之所以采用兩片 uPD42280芯片串聯是考慮到系統設定的同步范圍。對于 50HZ的PAL制的隔行掃描圖像,每一場的采樣像素點為32*32=1024個,只取其中 8位Y信號,則每一場的采樣數據量為 28800字節。uPD42280場存儲器的單片容量為 256K字節,可以容納約 256場。這樣采用兩片串聯增加了一倍的容量,采樣窗的數目可以達到512場。

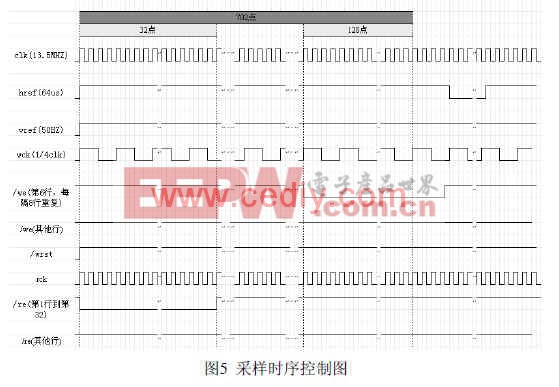

采樣的控制時序圖5所示,為了對 702*288的右1/4重疊區域進行行列的均勻采樣,每隔 8行在后128點進行 1/4clk均勻抽樣,得到 32點。同時,每場一共抽取 32行,這樣 FIFO中存儲數據為32*32=1024byte。而讀時鐘在每場的前 32行,采用clk(13.5MHZ)進行連續讀取。圖 6為一幀圖像重疊區域采樣的效果圖。本文引用地址:http://cqxgywz.com/article/191936.htm

2.2.4存儲器電路模塊設計

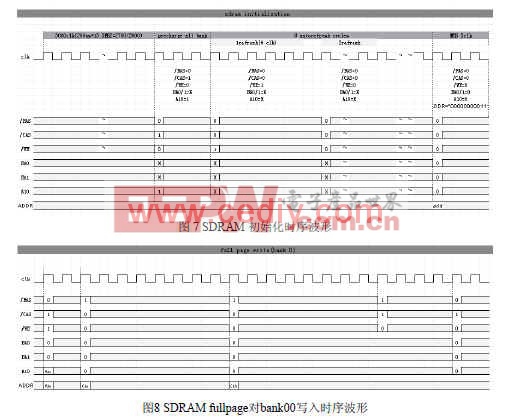

在本系統中,由于需要用到大規模的圖像數據存儲及運算存儲操作,并且考慮到系統算法的可擴展性,存儲器選取了兩片 SDRAM芯片 HY57V641620HG,每片 HY57V641620HG大小為 4bank*1M*16bit。在結構設計方面,由于 SDRAM不能夠同時進行讀寫操作,與主控運算電路采取并行連接的方式。這樣做的目的是可以進行 SDRAM的乒乓讀寫操作,提高數據讀取及寫入的效率。

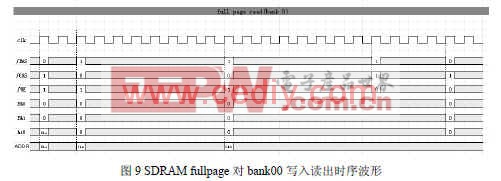

FPGA對SDRAM的初始化和fullpage模式下的讀寫控制的時序如圖 7、8、9。

2.2.5 FPGA主控運算電路模塊設計主控運算電路是本系統中最重要的硬件組成部分,因為這部分電路將承擔整個系統大部分控制和運算任務。這部分電路由 FPGA芯片 EP1C6及其附屬電路組成。

評論