基于FPGA的數字下變頻設計與實現

在擴頻通信中,數字下變頻(DDC)是一種很重要的技術,它包括數字混頻器、數控振蕩器以及數字濾波器三部分。而傳統的DDC大多采用專用芯片,雖然其外圍電路簡單、功能實現容易控制,但其大部分功能已經固化,存在兼容性較差、產品開發靈活性低、后續升級困難等缺陷。本文利用FPGA運算快速、易于升級等優點,在簡化算法的基礎上,用最短的時間進行混頻濾波得到兩路相交信號。用Verilog語言對整個下變頻進行行為描述建模,并給出相應的仿真綜合結果。

1 正交下變頻方案理論分析

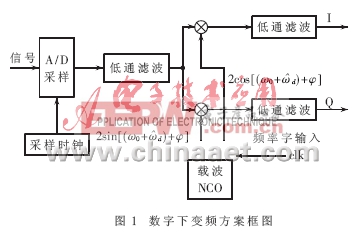

因為DDC的數據流是采樣信號的速率,DSP處理芯片很難完成高頻實時處理任務,而且FPGA中通常有大容量ROM資源,滿足查找表所需ROM資源,所以更適合用FPGA實現數字正交下變頻。數字正交下變頻是借助數控振蕩器NCO通過查找表的方式產生本地正交載波信號,與輸入信號進行正交混頻,經過低通濾波得到I―Q基帶信號。圖 1為其方案框圖。

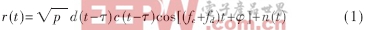

接收機收到的高頻信號表達式為:

式中, 為接收信號的幅值,d(t)為數據信息的波形, c(t)為偽碼波形,fc=891 MHz,fd=18.176 MHz為信號頻偏,n(t)為高斯白噪聲。根據帶通采樣定理,引入單位沖激函數δ(t)構成沖激函數P(t):

為接收信號的幅值,d(t)為數據信息的波形, c(t)為偽碼波形,fc=891 MHz,fd=18.176 MHz為信號頻偏,n(t)為高斯白噪聲。根據帶通采樣定理,引入單位沖激函數δ(t)構成沖激函數P(t):

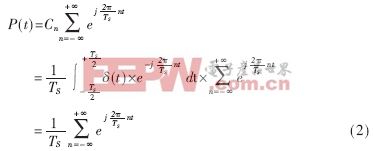

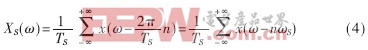

輸入信號為x(t),其傅里葉變換為x(ω),則用fS抽樣后得到抽樣信號可表示為:

由傅里葉變換性質得到XS(ω),可表示為:

由式(5)可知,A/D采樣使信號頻譜發生了周期延拓。中心頻率fC=891 MHz(如圖2)經帶通欠采樣后將信號頻譜搬移至fO=18.533 MHz。fO是fC除以fS后的余數。這樣A/D采樣實現了一個下變頻功能。

評論