寬帶載波電力線通信協議中信道交織的FPGA實現

摘要 介紹了寬帶載波電力線通信協議中用到的信道交織。在此協議的基礎上,提出了基于FPGA信道交織模塊的設計方案。文中對信道交織的物理層實現方法進行了介紹,該方法是通過ROM讀操作和RAM的讀寫操作來實現信道交織過程,較好地滿足了資源和時延的雙重要求。

本文引用地址:http://cqxgywz.com/article/201610/306124.htm隨著通信技術的不斷發展,出現了各種各樣的通信,一般有線通信和無線通信之分,有線通信一般是通過光纜電纜進行的通信,而無線則是通過電磁波進行空中信息傳遞的通信。雖然無線通信省缺了有形的傳輸媒介,通過空中接口進行通信,但無線通信在傳輸容量和傳輸質量都不如有限通信。電力線網絡覆蓋范圍廣,是其他網絡無法比擬的,而且是有限通信,通過電力線進行通信則成為研究重點,但電力線的初衷只是用來進行電力傳輸,還沒有考慮到用電力線進行信息的傳遞,所以原有電力線的鋪設導致電力線信道特性較差、干擾大、時變性差,不僅存在多徑時延問題,且存在頻率選擇性衰落的現象。隨著信號處理技術和信道調制技術的不斷發展,現在已經能克服這種電力線信道差的問題。其中的關鍵技術就是正交頻分復用(Orthogonal Frequency Division Multiplexing,OFDM),這是一種復用技術,同時是一種用多個相互正交的子載波來傳送信息的一種多載波調制技術。該技術可以解決電力線通信信道差的問題,大幅提高了平鋪利用率,并可實現電力線的有效通信。

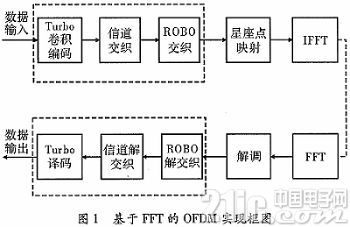

圖1是基于FFT的OFDM實現框圖。發送端:從數據鏈路層接收數據,經過一系列的信號處理和變換,以OFDM調制方式通過將信號發送到電力線。接收端:從電力線檢測到信號后,做相應的反向處理,最終將電力線上的載波信號還原為數據,送到數據鏈路層。在電力線通信系統中采取信道交織技術,在時間的維度上離散信道的突發差錯,從而使得有記憶信道可近似轉變為無記憶信道,使得設計的糾隨機差錯的糾錯碼同樣適用于多徑衰落信道。

1 信道交織的基本理論

信道交織的理論建立在香依理論的基礎上。Claude.E.Shannon提出:對于任意給定的有噪聲信道至少存在一種復雜的編碼方法,可使信道的傳輸速率無限逼近信道容量而同時保證傳輸差錯率達到任意小。而信道交織就是逼近這一相同理論的一種較好的實現方式。

信道交織的實質是一種置亂器,僅通過改變信息的結構來提高數據傳輸的可靠性。信道交織是通過把連續的比特信息分散開以避免突發差錯事件。這樣就能把錯誤的范圍盡量控制在糾錯電路的能力范圍之內。在接收端經過糾錯譯碼電路后,將這種置亂順序信息還原就能最大限度的的正確譯碼出發送的信息。

按照信道交織技術對于數據次序的改變規律,信道交織碼可分為周期交織和偽隨機交織兩類。周期交織又分為分組交織和卷積交織,周期交織指交織規律有明確的周期性,序列內數據之間的交織間隔恒定。所謂偽隨機交織,指交織不采用唯一的單個交織深度值而采用有變化的交織深度值,但變化仍有一定的規律。

2 電力線通信協議的信道交織實現

寬帶載波電力線通信協議中的信道交織過程包括信息位的交織、校驗碼交織、信息碼和校驗碼之間的交織,半字節移位4個步驟。具體的信道交織的過程如下:首先設定K代表信息bit的數量,N-K代表校驗bit的數量,K個信息bit會分成4個子塊,每個子塊的大小為K/4 bit,N-K個校驗bit會分成4個子塊,每個子塊的大小為(N-K)/4 bit,然后就是按步驟依次操作。

(1)信息位的交織。將信息bit存入一個K/4行4列的矩陣,依次把每列存滿。進行交織時每行的4個bit是同時讀出的。從這個矩陣讀出數據時,從第0 行開始,從第二次開始每次讀時行地址加上參數StepSize,這樣第一輪讀的行地址順序為(0,StepSize,2×StepSize,… [K/4]-StepSize),當讀了[K/4]/StepSize行之后,就讀到了矩陣的尾部,然后讀下一輪的行地址初始化為1,之后每次讀取時行地址加上參數StepSize,當讀了[K/4]/StepSize行之后又到了行尾,這樣第二輪讀的行地址順序為(1,1+StepSize,1+2 ×StepSize,…[K/4]-StepSize+1),然后第三輪的行地址加1為2,依次類推,經StepSize輪后全部行均已讀出。

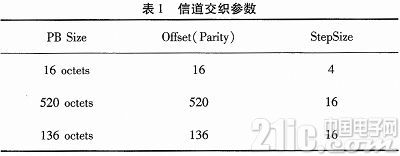

(2)校驗碼交織。校驗碼的交織與信息位的交織類似,只是每次讀行地址時均加一個偏移量。因此,校驗bit第一次讀從參數offset定義的行開始,步長參數還是StepSize,文中定義T=(N-K)/4,第一輪讀出的行的順序為(offset,(offset+StepSize)mod T,(offset+2×StepSize)mod T,…(T-StepSize+offset)mod T),然后第二輪第一行的指針加1,再重復作StepSize-1輪,最后經過StepSize輪,每輪讀出了T/StepSize行數據,一共讀出T行數據。表1列舉了信道交織中3種傳輸塊用到的參數。

(3)信息碼和校驗碼之間的交織。輸出的前4 bit為信息碼,接著4 bit為校驗碼,以此類推。

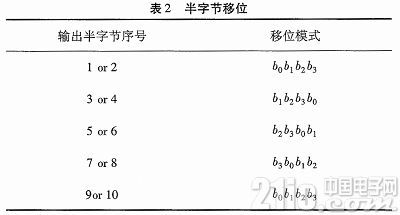

(4)半字節移位。半字節移位以4 bit為單位進行移位,無論信息bit還是校驗bit,每2個半Byte調整一次順序,表2列舉了具體移位模式。并且整體以32 bit為一個循環進行半字節移位操作。

3 電力線通信協議中信道交織設計

在寬帶載波電力線通信協議中信道交織處理的數據單元塊有3種:PB16,PB136和PB520。FPGA中信道交織主要有兩種實現方式:一是通過計數器和邏輯控制單元來實現;另一種是通過存儲在ROM中的信道交織表來實現。通過計數器和邏輯控制單元來實現,其中會涉及到大量的除法和取模運行,時間延遲大且不易控制。但采用存儲在ROM中的信道交織表來實現的話,只需通過Matlab計算出信道交織表的映射關系,然后將Matlab中的數據導出生成HEX 文件作為ROM的初始值。最后按ROM中存儲的地址寫到RAM即可實現信道交織。其中ROM和RAM直接調用Altera的IP核。考慮到后者只用通過 ROM讀和RAM讀寫就實現了信道交織,且邏輯簡單、時延小,所以本設計方案采用后者。且每種數據單元塊對應一張信息交織表,因此只需信道交織表就能滿足系統的要求。寬帶載波電力線通信協議中信道交織的FPGA實現就是采用存儲在ROM中的信道交織表來實現的方式。

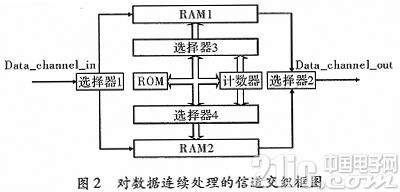

為了對數據進行連續處理,設計采用兩個RAM同時工作的方式,實現框圖如圖2所示。具體做法就是通過對兩個RAM的乒乓操作來實現數據的緩存和發送。在第 1個傳輸周期,在輸入端通過選擇器1將數據寫入RAM1。在第2個傳輸周期,在輸入端切換選擇器1將數據寫入RAM2,在輸出端同時將RAM1中的數據通過選擇器2讀出。在第3個傳輸周期,在輸入端切換選擇器1將數據寫入RAM1,在輸出端同時將RAM2中的數據通過選擇器2讀出。如此循環便可實現對數據的連續緩存和讀出。

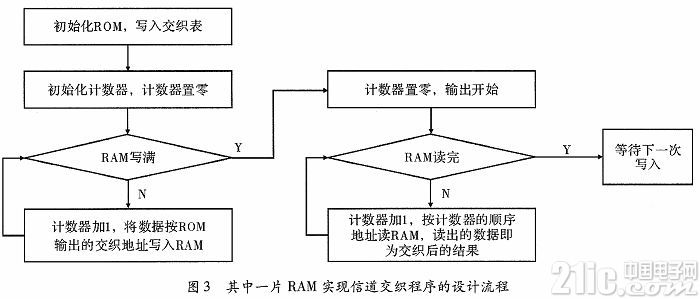

對其中一片RAM實現信道交織具體的實現過程就是通過控制ROM的讀出和控制RAM的讀寫來實現:在ROM中存放交織地址表,將RAM作為存放數據的緩存器,先將計數器的輸出送至ROM地址總線,選擇器再選擇從ROM讀出的交織地址送至RAM的地址線完成交織;然后按計數器的順序地址將RAM中的數據讀出,即為交織后的輸出結果。詳細的信道交織流程如圖3所示。

4 仿真結果分析

本文用Verilog HDL語言編程實現信道交織,并通過QuanusⅡ和Modelsim軟件進行仿真驗證。圖4為截取的一段仿真波形,波形顯示的是先按信道交織表的地址將輸入數據寫入RAM,輸入數據是連續的256個0,1比特流,最后按計數器的順序地址讀出交織后的數據,交織后的結果是前64個數據均為0,接著64個數據均為1,然后接著64個數據均為0,最后64個數據為1,與Matlab中的仿真結果一致,證明了該實現方案的正確性。

5 結束語

本文在寬帶載波電力線通信協議的基礎上,給出了基于FPGA的信道交織模塊的物理層實現方法。該方法從實際出發,權衡資源和時延的要求,實用性較強。其中,采用雙RAM可實現流水線操作,解決了單RAM等待的時延的問題;采用信道交織表的方式,相比單純采用邏輯控制的方式,可操作性和可移植性強。該方案已成功應用于某寬帶載波電力線通信模塊中,證明該方案切實可行。

評論