逆摩爾定律:以 12nm 專用化重塑半導體經濟學

導語(Lede)

如何把一篇以技術論證為主的論文,讀出一條清晰的“問題—方法—證據—結論”線?下面在保持原意不變的前提下,加入少量承接語與過渡句,幫助你在關鍵處“踩點”。

專用化的 12nm 芯片可以在深度學習任務上超越最先進的 7nm 與 5nm 技術,同時在成本和可持續性上帶來收益。(原文導語)

1. 核心問題與研究框架(Key Questions and Framing)

為了避免一上來就陷入指標與公式,我們先明確:作者想回答什么、采用怎樣的對比對象與邊界條件。只有把問題問準,后面的方法與結論才有落腳點。

在本節中,我們首先枚舉并解釋兩大關鍵問題的細微差別,以明確技術縮放在獨立于體系結構時所扮演的角色。隨后,我們說明研究的框架,包括選擇對比平臺以及若干簡化假設。最后,我們詳細描述所用工作負載、TDCC 術語,以及我們的建模與仿真方法。

1.1 研究問題(Questions)

我們要回答的兩個關鍵問題是:

**技術的角色是什么?**我們希望理解技術縮放所帶來的收益,以及新型晶體管能否、以及如何被新的芯片體系結構有效利用。

體系結構的角色是什么?我們希望理解是否可以通過體系結構變化,超越在 7nm 與 5nm 上實現的最先進(SOTA)芯片實現。為此,我們定義并評估一個可實施的 TDCC(Tiled Decoupled Control & Compute) 架構——Galileo,以實證回答第二個問題。

1.2 研究框架(Framing)

這部分相當于“讀者須知”:告訴我們用誰做標尺、在什么范圍內討論、以及時間與資源的現實約束。把這些前提放在明處,有助于你判斷后續推導是否站得住腳。

SOTA 平臺選擇。NVIDIA GPU 是深度學習訓練的主流且務實的選擇;按 NVIDIA 芯片供給緊張的報道,它們很可能也是數據中心推理的主流選擇。因此,我們把對齊乃至超越其性能作為目標。本研究關注大功耗數據中心芯片,不涉及 200W 以下的邊緣推理。

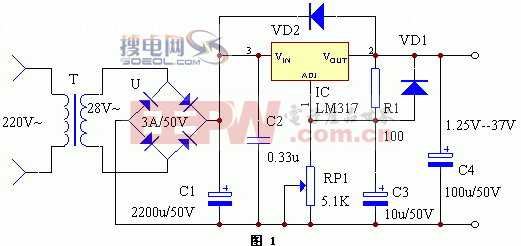

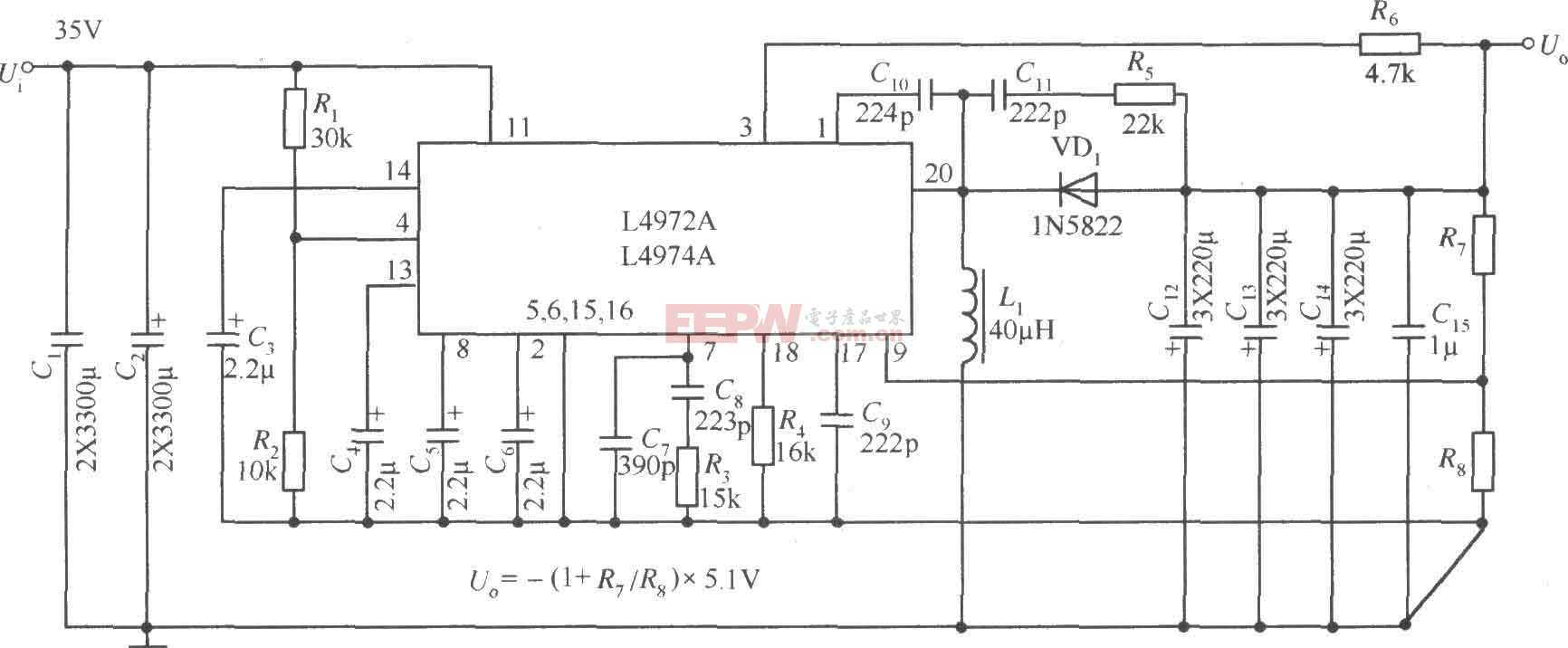

**開發時間線。**圖 1 展示了從 RTL 到芯片上板(bring-up)的開發流程,典型周期大約為 18 個月。這表明創建新芯片并非必須耗費多年,技術行業內的多類型組織均有能力完成。

**假設與邊界。**我們在工作負載選擇、算術制式、評測基線等方面作了明晰假設,以確保結論的可復現與可比較。

2. 技術與體系結構:定義、方法與結論預覽

有了問題與邊界,接下來先把“工具箱”亮出來:技術縮放如何估算、TDCC/Galileo 是什么,以及作者預期會得到怎樣的答案。你可以把本節當作“全書導讀”。

2.1 表 1:相對 12nm 的縮放估計(Wafer/Cost/Area/Power/Delay)

表 1 給出了相對 12nm 歸一化的估計:

晶圓價格:16nm=1.00,12nm=1.00,7nm=1.69,5nm=2.11,3nm=2.62;

晶體管成本:16nm=1.16,12nm=1.00,7nm=0.62,5nm=0.52,3nm=0.50;

面積縮放:16nm=1.16,12nm=1.00,7nm=0.40,5nm=0.22,3nm=0.14;

功率縮放:16nm=1.29,12nm=1.00,7nm=0.61,5nm=0.43,3nm=0.43;

延遲縮放:16nm=1.25,12nm=1.00,7nm=0.74,5nm=0.51,3nm=0.45。

注:所有數值均相對 12nm 歸一。

選擇 12nm 作為錨點有兩點原因:一是12/10nm 之后的成本縮放在逐節點上低于 18%;二是12nm 與相關地區/國家的出口限制門檻相對應。因此,在 12nm 上回答“能否通過專用化超越 5nm 或更先進節點的 SOTA”具備現實意義與普適價值。

2.2 TDCC 與 Galileo:概念與實例

先講概念再給實例,是為了讓讀者在看到后文的數據對比時,能把每一處差異對應到具體的架構選擇上,而不是僅停留在“誰更快”的表面。

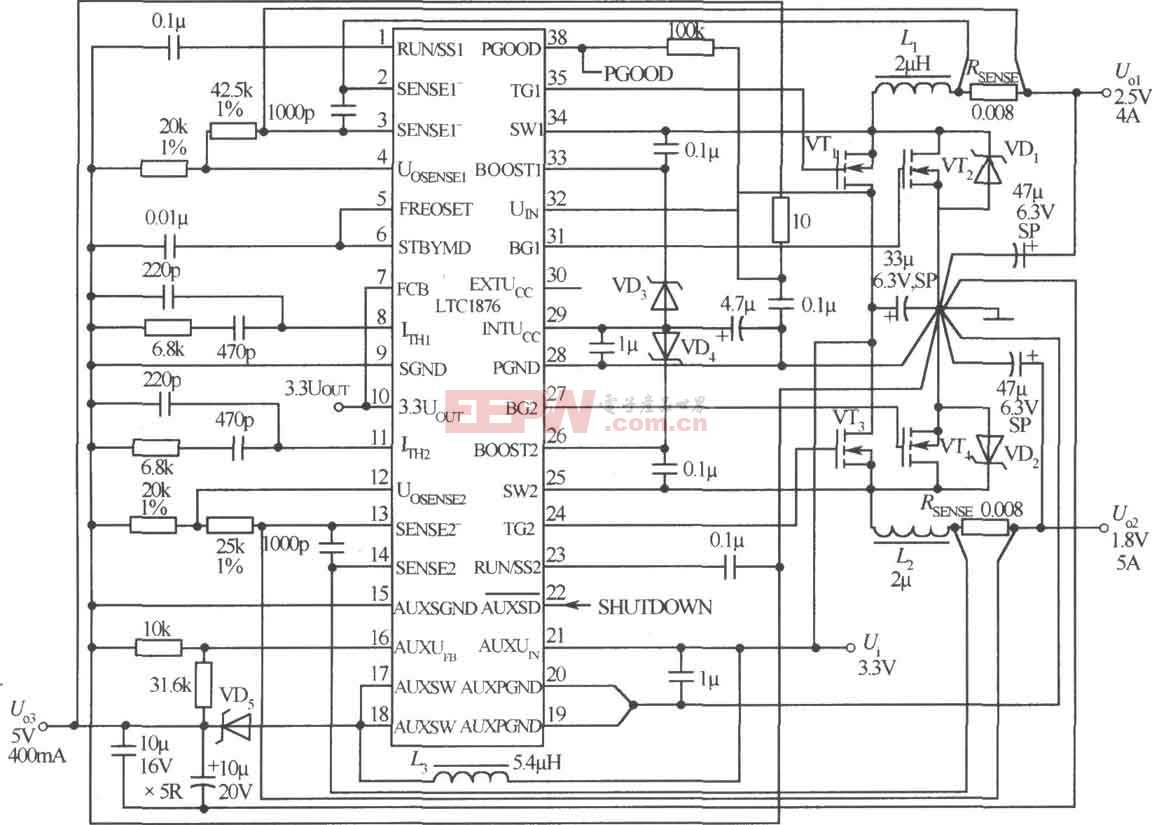

我們引入TDCC(平鋪化、解耦控制與計算)的體系結構概念,用以概括 AI 芯片架構從以矩陣引擎為核心到解耦數據搬運機制的演進。其一個具象化實現是Galileo,我們用它來承載實證結果。

結論預覽。

Answer 1(技術上限):在等面積/等頻等假設下,12nm→3nm 的應用級最佳加速約為 2.9×(以 LLM/Transformer 類負載為例),而 7nm→3nm 的最佳加速約 1.45×。工藝縮放的“紅利”顯著低于行業直覺。

Answer 2(架構收益):體系結構專用化可帶來約 2× 的帶寬節省與約 1.7× 的面積節省,并轉化為可觀的吞吐與能效收益。具體而言,12nm 的 Galileo 能顯著超越 7nm 的 A100,對 5nm 的 H100 也能實現小幅領先(具體取決于工作負載與算術專用化)。

3. 方法學:如何把“技術縮放”與“架構專用化”分解

從這一節開始進入“公式區”。別急著跳過:這些簡化的因子正是后面所有定量比較的“轉換器”,幫我們把不同工作負載落在同一把“尺子”上。

我們將應用操作粗分為三類:

帶寬主導(Bandwidth-bound),占比 (r_{bw});

計算主導(Compute-bound),占比 (r_c);

時延主導(Latency-bound),占比 (r_l)。

滿足 (r_{bw}+r_c+r_l=1)。

3.1 三類操作的速度因子

帶寬主導:由于外部帶寬(如 HBM2e/PHY)可在成熟節點實現,節點更替并不帶來“自然”帶寬提升,因此設 (s_{bw}=1)。真正的帶寬提升來自更合理的數據復用與片上存儲層級設計。

計算主導:

[

s_c = underbrace{text{計算面積密度提升}}{text{隨面積縮放}}timesunderbrace{text{等功耗頻率提升}}{text{隨延遲縮放}}

]

例如從 12nm→3nm:計算密度約 6.7×,等功耗頻率約 2.165×,因此 (s_capprox6.7times2.165approx14.5)。時延主導:建模為 (s_l=(a_c)^{gamma}),其中 (a_c) 表示可用于降低時延的有效芯面積縮放,(gammain[0.25,1])。對 DNN 來說 (r_l) 通常較小,阿姆達爾定律使 (gamma) 的影響受限。

3.2 “技術缺口”(Technology Gap)

圖 3 展示了在不同 (r_l)(例如 0.1 或近似為 0.01)以及不同 (gamma)(0.25/0.5/1)下,從 12nm→3nm 的可達加速。以 BERT 為例((r_capprox0.64),基本沒有顯著的時延主導算子),技術縮放所能提供的應用級加速上限為有限的數倍(約 2.9×),明顯低于工程直覺中的“多代合計 8×”。

4. TDCC:把“控制”與“計算”解耦、在 12nm 上做對

有了方法學的刻度,作者轉向體系結構層:為什么要解耦?解耦后能把“帶寬墻”搬哪里?這部分提供了后續 Galileo 設計取舍的由來。

思想要點。TDCC 將大規模矩陣算子引擎與數據搬運/控制分層、分塊、解耦:

以均質 tile 為基本單元:每個 tile 包含算子陣列與分布式片上存儲切片;

tile 之間通過 mesh NoC 互聯,減少集中式熱點;

全局調度與控制與計算資源解耦;

主機接口(如 PCIe/CXL)與 HBM 控制器/PHY 共構存儲與數據通道;

在軟件側,編譯器/運行時以塊級數據復用與按需搬運為目標對圖計算進行排程與布局。

工程收益。與通用 GPU 的 SIMT 機制相比,TDCC 去除了大量對 DL 并不關鍵的模塊(如大寄存器堆、FP64 單元等),使面積與功耗更集中地服務于數據運動與存儲復用,從而降低“帶寬墻”。

5. Galileo:TDCC 的具象實現與設計空間

從“理念”落到“樣機”。本節回答三個問題:怎么搭出來、能在哪些維度調參、不同應用的甜點位在哪。理解這里的“可調”對讀懂后文的對標非常關鍵。

我們在 12nm 節點上給出兩檔配置:

G7:面向對比 7nm A100;

G5:面向對比 5nm H100。

5.1 設計空間(Figure 5)

我們掃描了 SIMD 寬度、核心數、頻率(1–3 GHz,步長 100 MHz) 等參數組合,觀察到:

面積效率(TOPS/mm2) 可跨 5× 區間;

能效(pJ/op) 可跨 6× 區間;

不同應用(卷積主導 vs. GEMM 主導)對應不同的最優點。

這表明 TDCC/Galileo 不是“單點解”,而是一族可按任務定制的架構譜系。

5.2 G5 與 H100 的規格對照(節選)

總緩存(L1/L2/LLC):G5 為 120/60/32 MB;H100 為 29/-/50 MB(注:為對齊比較,文中將 NVIDIA 的 L2 記作 LLC);

HBM2e 容量/堆疊數:G5 32 GB / 4 棧;H100 80 GB / 5 棧;

幾何平均能耗(GM pJ/op):G5 0.53;H100 1.9。

6. 兩個答案:技術上限與架構紅利

前文鋪墊夠了,現在進入“論文要回答的兩道大題”。先給出技術縮放的上限,再展示架構專用化的硬回報,形成直觀對照。

6.1 Answer 1:技術縮放的“可達上限”

在我們設定的等面積、等功耗、等頻的建模框架下:

從 12nm→3nm:對 LLM/Transformer((r_capprox0.64, r_lapprox0.10))的最佳應用級加速約為 2.9×;對 MLPerf 代表負載約為 ~2.1×;

從 7nm→3nm:最佳應用級加速約 1.45×(LLM 檔)。

換言之,節點紅利遠小于“口口相傳”的線性外推。

6.2 Answer 2:架構專用化的“硬回報”

體系結構專用化可以:

節省約 2× 的帶寬需求;

在同等性能目標下節省約 1.7× 的面積;

進而在吞吐與能效上體現為可觀的提升。

系統對比結論:

在 12nm 上,Galileo 能顯著超越 7nm 的 A100;

相對 5nm 的 H100,G5 能實現小幅領先(取決于負載與算術策略)。

例外說明:在 BERT 訓練場景,G5 不及 H100,主要因為后者采用了透明 FP8 轉換等算術專用化(對 A100 可達 6.7× 加速)。這類增益與晶體管縮放無關,同樣可透明移植到 Galileo。

7. 存儲與帶寬:把“數據運動”當一等公民

這是全文的“抓手”段落:如果你只記住一件事,那就是算力未必是瓶頸,數據運動往往才是。因此,所有設計都要圍繞“少搬運、搬得值”展開。

節點獨立的帶寬:HBM2(e)/HBM3 的 PHY 與通道/棧數在 16nm 級即能實現,因此帶寬并不會因節點更替而“自然”提升。真正的帶寬提升來自tile 級復用、分層緩存與 NoC 編排。

匹配原則:以 G5 為例,先以目標算力確定算子陣列規模,再反推 HBM 棧數/通道、LLC/L2/L1 容量比例與 NoC 拓撲,使有效 pJ/op 壓至 0.53 檔,避免“算力空轉”。

8. 算術制式與數值專用化:FP8 的節點無關性

在系統層之外,數值層可以“加一把力”。把數據型做對(如 FP8/混合精度),帶來的往往是跨節點通用的收益。

窄數據類型(如 FP8/MSFP)的優勢與節點無關,體現在:

降低帶寬需求(更小數據寬度、更高緩存命中復用率);

提升計算密度(在相同面積/功耗下獲得更高算力)。

H100 在 BERT 訓練上的優勢主要來自此類算術專用化,同樣可以在 12nm Galileo 上引入。

9. 驗證流程:從分層畫像到系統對表

任何漂亮的結論都需要“復核路徑”。本節告訴你如何自己復現作者的過程:畫像→建模→對表→微基準校驗。

層級畫像:在 A100 上以 PyTorch + Nsight Systems 對代表網絡進行逐層時延/FLOPs/帶寬占比統計,得到 ((r_{bw},r_c,r_l));

對照標定:采用 NVIDIA 官方發布的 H100 相對 A100 的加速比與能效指標,校正模型參數;

微基準:選擇極端 GEMM 形狀(帶寬主導與計算主導)及若干時延主導算子,對模型在三類極端點的擬合進行驗證;

結果:模型對帶寬/計算主導類預測良好;對時延主導類,當 (gamma=0.25) 時與實測更吻合。

10. 產業含義:把資本投到“帶寬—存儲—互連—架構”

把技術結論放回商業與供應鏈語境:該投哪里、怎么排優先級。這部分幫助研發與管理在同一頁上溝通。

從“數據為王”到“數據運動為王”:當矩陣算力持續爬升,HBM/片上緩存/片間互連成為主導瓶頸,改造數據路徑的收益大于把相同架構簡單遷移至更先進節點。

工程可及性:約 18 個月 的“從 RTL 到上板”周期,意味著節點內代際的架構創新完全可行,無需等待每一代新節點窗口。

經濟與合規:在若干地區先進節點獲取受限的現實下,12nm 專用化可同時改善 TCO 與碳足跡,并提升半導體產業的經濟生產率。

11. 結論(Conclusions)

最后收束全文主線:為什么“12nm 專用化”不是權宜之計,而是技術、經濟與合規三條線同時成立的方案。閱讀到這里,前面的數據與方法會自然拼成一張圖。

經驗被刷新:對主流深度學習負載,工藝縮放(如 12nm→3nm)的應用級紅利上限僅為數倍(LLM 檔約 2.9×),遠低于行業直覺;

路線更清晰:在 12nm 這類成熟節點上,只要體系結構專用化做對,完全可以對齊甚至小幅超越 7/5nm 的 SOTA(A100/H100),而且能效收益更集中;

執行建議:把帶寬/存儲/互連與數據復用作為一等設計目標;將 FP8 等算術專用化作為“透明層”植入;以 tile/NoC/緩存層級 的共設計來閉環系統。

評論