穩壓器詳解:如何從你的 LDO 中榨取最佳性能

低壓差(LDO)穩壓器是一種簡單、經濟的器件,可將較高的輸入電壓轉換為穩定的輸出電壓。其固有噪聲極低,因無開關瞬態干擾,且幾乎無需外接元器件,占用電路板空間極小。

LDO 開箱即可便捷使用,但這并不意味著其性能已達上限。本文將回顧標準穩壓器與 LDO 的工作原理,并探討幾種提升其噪聲性能的方法。

從標準穩壓器到 LDO 的演變

線性穩壓器的能效偏低,因其需通過調整穩壓器件的功耗來穩定輸出電壓,穩壓器件通常為功率晶體管 —— 雙極型晶體管或場效應晶體管(FET)。

1. 基本的PMOS和NMOS線性調節器架構。

圖 1 展示了采用 P 型金屬氧化物半導體場效應管(PMOS)和 N 型金屬氧化物半導體場效應管(NMOS)的 MOSFET 線性穩壓器電路。兩種電路中,穩壓器功率晶體管的漏源極電壓均滿足:

VDS = V輸入 - V輸出 = I輸出 × RDS

其中,漏源極電阻(RDS)的阻值取決于場效應管的柵源極電壓(VGS)。

穩壓器的控制電路通過電阻 R1 和 R2 對輸出電壓進行分壓,將分壓值與基準電壓(VREF)做比較,產生的誤差信號驅動場效應管的柵極電壓(VG),進而調控柵源極電壓,以抵消負載電流(IOUT)或輸入電壓(VIN)變化對輸出電壓的影響。在這些基礎設計中,柵極電壓的調節范圍介于誤差放大器的正負電源軌之間,即輸入電壓和地電位。

漏源極電壓的最小允許值被稱為壓差(VDO)。穩壓器正常工作時,需滿足輸入電壓 ≥ 輸出電壓 + 壓差。若輸入電壓低于該值,穩壓器將脫離穩壓狀態,無法維持預設輸出電壓,此時輸出電壓會隨輸入電壓變化,始終等于輸入電壓減去壓差。

顧名思義,LDO 的設計初衷就是最大限度降低壓差,目前主流的 LDO 器件可實現低至 100 毫伏的壓差穩壓輸出。隨著低電壓、高能效設計的普及,LDO 已成為當下主流的線性穩壓器類型。

那么,如何將標準穩壓器設計改造為 LDO?在設計階段,增大功率場效應管的尺寸可降低漏源極電阻,從而減小壓差,但電路架構才是決定壓差的核心因素,尤其是柵源極電壓的最大和最小值范圍。

PMOS 架構的穩壓器工作時,柵源極需施加負電壓:當輸入電壓或負載電流升高時,控制電路會進一步降低柵極電壓,使柵源極負壓增大。在 PMOS 電路中,源極電壓(VS)等于輸入電壓,當柵極電壓被拉至負電源軌時,柵源極負壓達到最大值,即VGS = - 輸入電壓。減小壓差(輸入電壓 - 輸出電壓)并不會影響柵源極負壓的幅值,因此 PMOS 架構更易實現 LDO 設計。

NMOS 架構的情況則截然相反:當輸入電壓降低時,控制電路需提高柵極電壓,增大柵源極正電壓。誤差放大器的柵極電壓調節范圍仍為輸入電壓至地電位,但此時源極電壓等于輸出電壓,因此柵源極電壓的最大值為輸入電壓 - 輸出電壓,即場效應管的漏源極電壓。

場效應管的柵源極電壓需高于約 2 伏的閾值電壓才能導通,這使得上述基礎 NMOS 架構穩壓器的最小壓差被限制在 2 伏,遠達不到 LDO 的設計要求。

在輸入電壓與誤差放大器正電源軌之間增加內置電荷泵,可解決這一問題(圖 2)。電荷泵能抬升誤差放大器的正電源軌電壓,使其能輸出更高的柵源極電壓,從而實現 NMOS 架構的 LDO 設計。另一種實現方式是通過外部偏置引腳(BIAS)為誤差放大器提供更高的正電源軌,德州儀器新款超低壓差 LDO 便采用了這一方案。

2. 這里,對基本NMOS電路進行修改以支持LDO工作。可以使用充電泵或外部偏置電壓。

如前所述,低噪聲是線性穩壓器和 LDO 的核心優勢,許多應用中都會采用 LDO 對開關電源的噪聲輸出進行濾波處理。器件數據手冊中有兩個參數用于表征 LDO 的噪聲性能,接下來將對其展開分析。

輸入噪聲與電源抑制比

電源抑制比(PSRR) 也被稱為電源紋波抑制比,用于衡量 LDO 抑制輸入側外部噪聲(如開關電源產生的噪聲)的能力,其數值為特定應用頻率范圍內,LDO 輸出紋波與輸入紋波的比值。圖 3 為 TPS717 的電源抑制比隨電流變化的曲線,該器件是一款低噪聲、高帶寬電源抑制比的 LDO,最大輸出電流為 150 毫安。

3. TPS717 采用高帶寬、高增益的誤差環路增益,以實現高 PSRR。

電源抑制比的單位為分貝(dB),數值越高,噪聲抑制能力越強,計算公式為:

有多個因素會影響電源抑制比:負載電流增大時,對高低頻段的電源抑制比都會產生影響。場效應管的輸出阻抗與漏極電流成反比,因此負載電流增大會降低誤差環路增益,導致低頻段電源抑制比下降;同時,負載電流增大還會使輸出極點向高頻段偏移,拓寬反饋環路的帶寬,從而提升高頻段的電源抑制比。

當漏源極電壓低于約 1 伏時,場效應管會從有源(飽和)工作區過渡到三極管 / 歐姆區,導致反饋環路增益下降,電源抑制比也會隨之降低。

對比不同 LDO 的電源抑制比性能時,需保證輸入電壓 - 輸出電壓的差值和負載電流一致;同時,由于低輸出電壓下的電源抑制比通常更優,還需對比輸出電壓相同的 LDO 器件。

輸出噪聲與頻譜噪聲密度

LDO 本身并非無噪聲器件,其內部會產生固有噪聲,疊加在上述殘余輸入噪聲上并體現在輸出端。LDO 及其他電子器件的固有噪聲由多種物理機制產生:

熱噪聲:有源和無源器件中均會產生,由導體中電荷載流子(電子或空穴)的隨機熱運動引起,與絕對溫度成正比,與電流無關,屬于頻譜平坦的白噪聲;

閃爍噪聲:僅存在于有源器件中,特性隨制程工藝變化,與電流成正比,與頻率成反比,因此也被稱為 1/f 噪聲;

散粒噪聲:由電子或空穴隨機穿過 PN 結等勢壘引起,與電流相關,頻譜同樣平坦。

固有噪聲的單位為微伏 / 根號赫茲(μV/√Hz),LDO 數據手冊中會通過輸出頻譜噪聲密度曲線 表征噪聲隨頻率的變化規律,通常還會提供多條曲線,展示輸出電流、輸出電壓等參數對輸出噪聲的影響。

圖 4 為某款 1 安培高精度低噪聲 LDO 的頻譜噪聲密度隨輸出電壓變化的曲線,該器件的最大壓差為 200 毫伏。

4. 隨著低頻的VOUT增加,LDO的頻譜噪聲密度會增加。

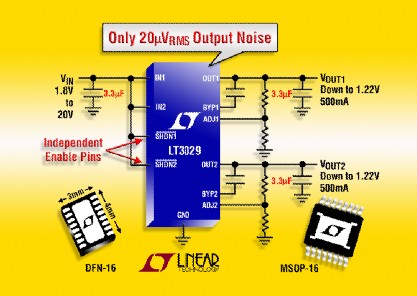

LDO 的輸出噪聲主要集中在低頻段,為方便對比,數據手冊中通常會給出一個綜合噪聲值,即10 赫茲至 100 千赫茲頻率范圍內的輸出噪聲積分值,單位為微伏均方根(μVRMS)。以此為指標,TPS7A91 的輸出噪聲為 4.7 微伏均方根。

對比不同廠商的器件時需注意:部分廠商的數據手冊會選擇其他頻率范圍進行噪聲積分,如 100 赫茲至 100 千赫茲,甚至自定義積分范圍。選擇特定頻率范圍積分可能會掩蓋器件的不良噪聲特性,因此除了關注積分值,還需仔細查看各頻段的噪聲曲線。

提升 LDO 噪聲性能:從基準電壓電路入手

如何提升標準 LDO 的噪聲性能?盡管 LDO 的所有元器件都會產生噪聲,但基準電壓電路 是主要的噪聲源,原因有二:其一,該電路包含多個易產生噪聲的有源和無源器件;其二,基準電壓上的任何噪聲都會被誤差放大器放大,輸入至基準電壓的紋波也會被放大并體現在輸出端。因此,帶隙基準電路不僅要具備低噪聲特性,還需擁有高電源抑制比。

解決內部噪聲和電源抑制比問題的簡單方法,是在帶隙基準電路的輸出端串聯一個低通濾波器(LPF)。如圖 5 所示,可通過在原有內置電阻 RNR/SS 上外接電容 CNR/SS 構成低通濾波器,許多低噪聲 LDO 都專門設置了對應的引腳。

5. 添加降噪電容(1)和前饋電容(2)可以提升LDO噪聲性能。

該電容具備雙重功能:LDO 上電初期,誤差放大器檢測到的基準電壓會隨電容通過內置電阻充電而逐漸上升,換言之,低通濾波器實現了軟啟動 功能,這也是電阻和電容下標標注 “NR/SS(噪聲抑制 / 軟啟動)” 的原因。若 LDO 上電時需要為大容量輸出電容充電,軟啟動功能可有效避免電路進入限流狀態。

低通濾波器并非萬能:其會讓帶隙基準電路的低頻紋波通過,導致 LDO 低頻段的電源抑制比下降。采用低等效串聯電阻(ESR)的陶瓷輸出電容,可改善電源抑制比性能,電容容值需根據應用的關鍵工作頻率選擇;同時,合理的電路板布局設計,能減少電路板寄生參數導致的輸入紋波向輸出端的串擾。

另一項防止輸出噪聲被誤差放大器放大的策略,是增加前饋電容(CFF)。前饋電容可對電阻 R1 進行交流旁路,在保持直流增益不變的前提下,降低電路的高頻增益。

增加前饋電容會對 LDO 的多項性能產生積極影響,包括噪聲性能、穩定性、負載響應和電源抑制比,同時還能提高反饋環路的相位裕度,改善 LDO 的負載瞬態響應,減少振蕩并縮短建立時間。

標準三端固定輸出 LDO 的電阻 R1/R2 分壓節點集成在器件內部,無法外接前饋電容,但許多專為低噪聲設計的 LDO 會將該節點引出為引腳。當然,可調輸出 LDO(如圖 6、7 中的 TPS7A91)均配備反饋引腳(FB),可外接分壓電阻和前饋電容,該器件還設有噪聲抑制 / 軟啟動電容引腳(CNR/SS)。

6. TPS7A91是一種可調輸出的低噪聲運行型LDO。

7. 添加前饋電容CFF可改進在低頻下的輸出噪聲表現。

下表總結了上述兩種噪聲抑制方案(噪聲抑制電容、前饋電容)在不同頻率段對 LDO 性能的影響。

總結

LDO 是目前線性穩壓領域的主流架構。本文介紹了兩種主流的場效應管 LDO 架構,分析了 LDO 的噪聲來源,并闡述了提升其噪聲性能的實用方法。如需深入了解 LDO 噪聲相關知識、電源抑制比詳細解析,或前饋電容的應用技巧,可參閱相關專業資料。

德州儀器現提供超過 500 款適用于不同應用場景的 LDO 器件,為設計人員提供豐富的性能選擇,包括低噪聲、寬輸入電壓、小封裝、低靜態電流以及處理器專用型等各類器件。

評論