恩智浦?jǐn)U大Arteris片上網(wǎng)絡(luò)部署,助力邊緣AI架構(gòu)規(guī)模化擴(kuò)展

隨著邊緣 AI 系統(tǒng)向集中化、高算力密度方向發(fā)展,片上數(shù)據(jù)傳輸正日益成為架構(gòu)瓶頸。恩智浦(NXP)擴(kuò)大對(duì) Arteris 片上網(wǎng)絡(luò)(NoC)與緩存一致性互連 IP 的部署,凸顯出一個(gè)行業(yè)大趨勢(shì):互連架構(gòu)已成為核心設(shè)計(jì)挑戰(zhàn),不再只是簡(jiǎn)單的 “布線”。

Arteris 近期宣布,NXP 將在其多款 AI 芯片平臺(tái)上擴(kuò)大使用FlexNoC?、Ncore?、CodaCache? 及 Magillem? 集成自動(dòng)化工具。這看似是一次常規(guī)的 IP 擴(kuò)展合作,實(shí)則具有戰(zhàn)略意義 ——NXP 正圍繞可擴(kuò)展互連基礎(chǔ)設(shè)施進(jìn)行標(biāo)準(zhǔn)化,以支撐日益異構(gòu)化、安全關(guān)鍵型的邊緣 AI 設(shè)計(jì)。

真正的挑戰(zhàn):邊緣側(cè)的異構(gòu)擴(kuò)展

過去十年,汽車與工業(yè)級(jí) SoC 發(fā)生了巨大轉(zhuǎn)變。原本基于分布式 MCU 的系統(tǒng),正演變?yōu)?strong>集中式計(jì)算平臺(tái),集成了:

高性能應(yīng)用 CPU

實(shí)時(shí)安全內(nèi)核

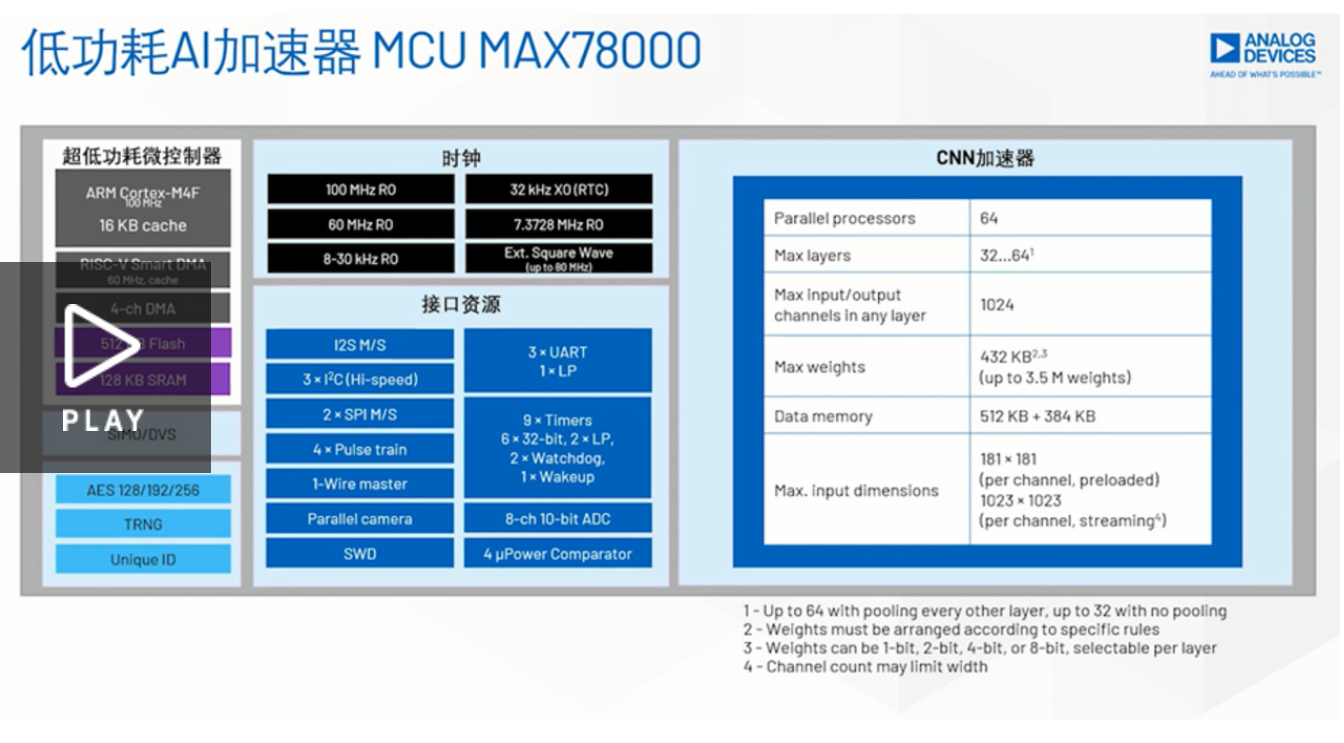

NPU 與 AI 加速器

GPU 與視覺處理器

安全隔離區(qū)

高帶寬內(nèi)存子系統(tǒng)

這種高度異構(gòu)性給片上互連帶來巨大壓力。傳統(tǒng)基于總線的互連架構(gòu),無法高效擴(kuò)展以支持高核心數(shù)、重加速器負(fù)載與混合關(guān)鍵度流量。

邊緣 AI 工作負(fù)載(如傳感器融合、ADAS 感知、工業(yè)機(jī)器視覺、預(yù)測(cè)性維護(hù))需要確定性低延遲、持續(xù)帶寬,以及安全域與非安全域之間的嚴(yán)格隔離。同時(shí),能效仍是硬性約束。

而可配置片上網(wǎng)絡(luò)(NoC)架構(gòu),正是解決這些問題的關(guān)鍵。

FlexNoC:片上數(shù)據(jù)傳輸?shù)墓歉?/strong>

NXP 擴(kuò)大使用 Arteris FlexNoC,表明其持續(xù)采用分組式、可擴(kuò)展互連架構(gòu)。

FlexNoC 支持自定義拓?fù)洌壕W(wǎng)格、分層、交叉開關(guān)或混合結(jié)構(gòu),可根據(jù)負(fù)載特性量身定制。這種靈活性在 SoC 集成流量模式差異極大的計(jì)算集群時(shí)至關(guān)重要:

AI 加速器產(chǎn)生突發(fā)、高帶寬事務(wù)

實(shí)時(shí)內(nèi)核要求低延遲確定性

安全子系統(tǒng)需要嚴(yán)格隔離

細(xì)粒度服務(wù)質(zhì)量(QoS)、帶寬分配與流量整形能力,可讓架構(gòu)師在互連層直接執(zhí)行策略。這對(duì)符合 ISO 26262 功能安全的汽車設(shè)計(jì)至關(guān)重要,必須保證隔離性與行為可預(yù)測(cè)性。

在集中式域控制器架構(gòu)中,NoC 不再只是連接層,而是整個(gè) SoC 的性能調(diào)控核心。

可擴(kuò)展一致性,不帶來功耗爆炸

NXP 采用 Arteris Ncore? 緩存一致性 NoC IP,也反映出多核與異構(gòu)一致性域復(fù)雜度的不斷提升。

隨著邊緣設(shè)備采用更多核心、集成更多加速器,維持高效硬件一致性變得愈發(fā)困難。基于廣播的偵聽協(xié)議在大規(guī)模擴(kuò)展時(shí),會(huì)因功耗與帶寬開銷劇增而不再適用。

Ncore 采用基于目錄的一致性與分布式偵聽過濾,可減少無效流量,同時(shí)支持可擴(kuò)展的一致性域。對(duì)于 CPU 與加速器必須共享內(nèi)存空間的異構(gòu)計(jì)算集群而言,這一點(diǎn)至關(guān)重要。

替代方案(軟件管理一致性或非一致性分區(qū))通常會(huì)增加延遲與設(shè)計(jì)復(fù)雜度。對(duì)多數(shù)高性能邊緣 AI 負(fù)載來說,硬件管理一致性仍是最高效路徑。

內(nèi)存壓力與 CodaCache 的作用

邊緣 AI 工作負(fù)載往往是內(nèi)存密集型的。傳感器融合流水線與神經(jīng)網(wǎng)絡(luò)推理引擎會(huì)產(chǎn)生大量 DRAM 訪問流量,而外部?jī)?nèi)存在功耗、延遲與成本上代價(jià)高昂。

CodaCache? 末級(jí)緩存 IP 通過提升有效內(nèi)存利用率,緩解片外帶寬壓力。可配置相聯(lián)度、分區(qū)與 QoS 感知策略,可實(shí)現(xiàn)安全域之間的性能隔離,同時(shí)減少 DRAM 訪問次數(shù)。

在汽車 ECU、工業(yè)控制器等熱受限場(chǎng)景中,減少片外內(nèi)存訪問直接帶來能效提升與系統(tǒng)可靠性改善。

為小芯片(Chiplet)與長(zhǎng)期可擴(kuò)展性做準(zhǔn)備

此類合作中常被忽視的一個(gè)戰(zhàn)略層面,是未來封裝方向。

現(xiàn)代 NoC 架構(gòu)越來越多地考慮多裸片可擴(kuò)展性。清晰的分區(qū)邊界、協(xié)議抽象與模塊化網(wǎng)絡(luò)接口單元(NIU),讓互連架構(gòu)可跨裸片接口擴(kuò)展,適配小芯片趨勢(shì)。

對(duì)于像 NXP 這樣擁有長(zhǎng)周期汽車產(chǎn)品的公司而言,選擇同時(shí)支持當(dāng)前單片 SoC 與未來異構(gòu)封裝策略的互連 IP 廠商,可降低長(zhǎng)期架構(gòu)風(fēng)險(xiǎn)。

集成復(fù)雜度已成新瓶頸

值得注意的是,NXP 繼續(xù)采用 Arteris Magillem? 實(shí)現(xiàn)IP 集成自動(dòng)化。

當(dāng) SoC 集成數(shù)百個(gè) IP 模塊時(shí),配置管理、接口驗(yàn)證與寄存器映射成為繁重的工程負(fù)擔(dān)。基于 IP?XACT 流程的元數(shù)據(jù)自動(dòng)化,可提升復(fù)用率、減少集成錯(cuò)誤,對(duì)需要可追溯性與文檔完備性的安全認(rèn)證項(xiàng)目尤為重要。

如今,集成復(fù)雜度已與微架構(gòu)復(fù)雜度相當(dāng)。自動(dòng)化工具不再是可選的效率提升手段,而是風(fēng)險(xiǎn)控制必備工具。

更大的行業(yè)趨勢(shì)

NXP 擴(kuò)大部署 Arteris 產(chǎn)品,反映出整個(gè)半導(dǎo)體行業(yè)的轉(zhuǎn)變:

互連已成為戰(zhàn)略架構(gòu)層

一致性擴(kuò)展既是性能問題,也是功耗問題

內(nèi)存效率是 AI 性能的核心

集成自動(dòng)化正變得至關(guān)重要

隨著 AI 工作負(fù)載從云端走向邊緣,汽車架構(gòu)向集中計(jì)算演進(jìn),可擴(kuò)展、可配置的 NoC 基礎(chǔ)設(shè)施成為底層基石。

總結(jié)

對(duì)半導(dǎo)體架構(gòu)師而言,這一趨勢(shì)提醒我們:未來 SoC 的競(jìng)爭(zhēng)力,不只取決于計(jì)算 IP 的選擇,更取決于模塊間數(shù)據(jù)傳輸?shù)男?/strong>。

在 AI 時(shí)代,互連架構(gòu)就是系統(tǒng)架構(gòu)本身。

評(píng)論