硅光子技術:點亮更高效數據中心之路

核心要點

光子互連有望提升帶寬密度,同時顯著降低功耗,AI 算力需求正推動其在數據中心落地應用。

但光子互連需整合多種異質材料,帶來工藝兼容性、熱應力與機械應力等難題。

集成電光 I/O 模塊是終極目標,前提是攻克其設計與工藝挑戰。

光纖傳輸信號比銅線更快、更高效,已成為全球通信網絡的首選介質。在數據中心機架間、板間等短距場景,工程師希望將光學元件微型化,以釋放光纖帶來的節能優勢。

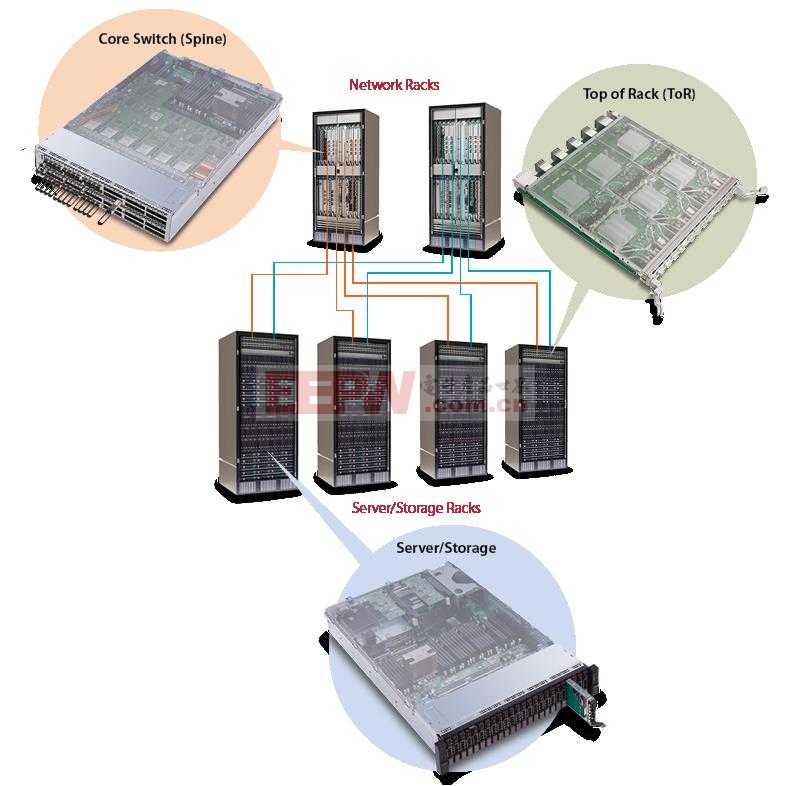

AI 算力負載與其他高性能計算(HPC)負載的核心差異在于數據傳輸量。大語言模型(LLM)查詢在用戶與數據中心之間的 “南北向流量” 與傳統搜索相近,但數據中心內部的 “東西向流量” 要大得多。GPU 集群與單顆 GPU 需對超大規模數據陣列執行簡單乘加運算,而帶寬瓶頸不僅限制整體性能,也是功耗的主要來源。

去年被 AMD 收購的硅光子初創公司 Enosemi 在白皮書中估算,前沿高性能專用集成電路(ASIC)近一半功耗消耗在數據傳輸環節。

格芯(GlobalFoundries)首席商務官邁克?霍根提出,決定互連效率的四大關鍵指標:

傳輸距離:信號無需放大即可傳輸的長度;

帶寬密度:單位面積傳輸比特數;

能效:單位能耗傳輸比特數;

計算效率:計算資源的整體利用率。

在短距場景中,光學元件尺寸偏大限制了帶寬密度。要兌現光子互連的節能價值,光學元件必須與所連接的電子電路同步微型化。

為此,行業正探索三種技術路線:

可插拔組件:尺寸較大、模塊化、易集成,但需較長連線連接控制電路,適合板間、機架間及數據中心跨區連接。

共封裝光學(CPO):將分立光學元件與電子控制電路集成,通常采用引線鍵合連接。

光 I/O(OIO)模塊:將光、電芯片合為一體,整體表現如單一部件。

光子互連核心組件

無論尺寸大小,光子互連的基礎組件一致:

光源:數據中心場景主流采用磷化銦(InP)激光二極管。激光器件需承受更高電流與溫度,是光子電路中可靠性最弱的環節;封裝前篩選合格激光器至關重要,可插拔組件的優勢在于便于更換故障激光器。

調制器:將連續激光轉換為數據比特流,決定傳輸速率。比利時微電子研究中心(imec)在 2025 年 IEEE 電子器件會議(IEDM)指出,鈮酸鋰(LiNbO?) 可實現超 100GHz 帶寬,高效低損,但尺寸大且存在鋰污染風險,不適合與硅直接集成。新加坡研究團隊通過微轉移印刷技術,將圖案化鈮酸鋰調制器轉移到硅基底,避免直接生長帶來的污染。而 CPO 尤其是 OIO 方案更常用硅基諧振器,通過加熱器調控摻雜硅環的折射率實現調制。

NLM 光子技術公司 CEO 布拉德?布斯表示,硅并非高效調制材料,替代方案仍在探索中。該公司方案是將發色團摻入小分子有機玻璃,通過相鄰硅器件實現電場開關調控。

波導:傳輸調制后的光信號,硅在目標波段下是低損耗優質波導材料。CPO 與 OIO 集成模塊采用硅基或有機中介層,可內嵌光子組件。

光電探測器:鍺(Ge) 是適配的探測器材料。

耦合器:負責在不同折射率材料間傳遞光信號,耦合損耗占系統總損耗比例較高。耦合方式包括光纖貼靠光源、聚合物橋接間隙等,設計需避免光學缺陷,實現折射率漸變過渡。

光學電路需配套控制電路驅動調制器、處理探測器信號等。縮短控制電路與光學元件的距離,可提升性能、降低功耗。

圖 1:硅光子學的基本構建模塊。(a) 單偏振光柵耦合器,(b) 微環調制器,(c) 微環調制器的耦合間隙,(d) 雙微環諧振器。

光電集成挑戰

異質集成的核心目標就是縮短互連距離,集成光學面臨的諸多問題與先進封裝共性問題一致:單個組件技術成熟,但低成本規模化連接是難點。

光電融合還帶來新挑戰:

法國原子能委員會電子與信息技術實驗室(CEA-Leti)在硅中介層中嵌入波導等硅光子組件,需預留光路連接表面激光器與探測器,同時通過硅通孔(TSV)連接調制器與封裝底部。但這些結構產生的機械應力會引發光學畸變、增加損耗,因此中介層與系統級封裝設計工具必須能模擬熱應力與機械應力的光電雙重影響。該團隊研發負責人讓?沙博尼耶表示:“我們必須自定義設計規則,實現光電元件混合集成。”

調制器依賴加熱器調控諧振頻率,通過熱隔離可顯著節能。

鍺探測器可直接在硅上外延生長,但所需厚鍺層與先進晶體管的超薄硅鍺納米片工藝不兼容,鍺外延成本可占電路總成本的 40%。

科研場景中,磷化銦激光器通常單獨制備,通過微轉移印刷貼裝到中介層,小批量處理便于篩選合格器件;商用規模化方案方面,日本 NTT 團隊實現磷化銦晶圓與硅晶圓鍵合,原位生長銦鎵砷磷(InGaAsP)激光器。

電路的電子部分可在標準 CMOS 產線制造,通過銅 hybrid bonding 與中介層連接,設計中同樣需考慮光學元件的熱應力與機械應力。

盡管面向硅電路同步縮放的全集成光子互連仍需大量研發,但行業目標高度一致。霍根表示:“計算廠商、網絡龍頭與硅供應商已形成共識 ——東西向流量規模化必須依靠光學互連。”

評論