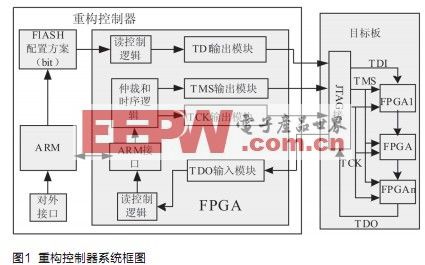

- 為充分利用硬件資源,滿足不同的應用需求,本文提出了一種基于JTAG邊界掃描模式配置的重構控制器,詳細介紹控制器的硬件實現以及配置流程,該控制器通過模擬JTAG接口時序及TAP狀態機的功能,實現在系統配置目標可編程器件。

- 關鍵字:

FPGA TAP狀態機 JTAG邊界掃描 重構 201001

- 隨著2010年的來臨,當今的全球電子公司紛紛做出明智而審慎的研發投資決定,以便借助創新的新產品,快速抓住新的市場機遇。FPGA越來越多地成為這些公司成功的關鍵。除了少數可超大批量生產的商品外,應用ASIC的高成本和高風險無法讓絕大多數的商品贏利;現在面臨著加速替代ASIC所帶來的機遇,這主要體現在以下不同方面:芯片體系結構,也就是能夠推出某種架構和相關的I/O,而且,密度和性能還能夠達到一定水平,從而可以替代ASIC的功能。 軟件在加速替代ASIC過程中也扮演了重要角色。高效的軟件和設計工具大大提高了

- 關鍵字:

賽靈思 FPGA ASIC 摩爾定律

- 據業者透露,臺積電公司將于今年中期開始為Altera公司生產28nm制程FPGA芯片產品。這種FPGA芯片將集成有28Gbps收發器,產品面向云計算,在線存儲以及移動視頻等應用,Altera公司兩年前曾推出該系列產品的 40nm制程版本。臺積電還宣布其28nm制程將為全代制程(full node:即制程升級時需要對芯片電路進行重新設計),而且年內其28nm制程還將具備可按客戶的需求制作出HKMG(High-K絕緣層+金屬柵極)或SiON(SiON絕緣層+硅柵極)這兩種不同柵極結構的能力.

臺積電

- 關鍵字:

臺積電 28nm FPGA Altera

- 理解FPGA 中的壓穩態 本白皮書介紹FPGA 中的壓穩態,為什么會出現這一現象,它是怎樣導致設計失敗的。介紹怎樣計算壓穩態MTBF,重點是對結果造成影響的各種器件和設計參數。

引言

當信號在不相關或者異步時鐘域

- 關鍵字:

FPGA 壓穩態

- 人們對寬帶服務的帶寬要求越來越高,促使芯片供應商使用更多的高速串行收發器。因此,下一代應用采用了多種數據速率,從幾Mbps 到數百Gbps,在一種設備中集成了多種協議和服務。以太網等迅速發展的標準以及對提高

- 關鍵字:

FPGA ASIC 40 nm

- 介紹了基于SOPC技術的嵌入式數字圖像處理系統的設計方法,該系統以Alteral公司的Nios嵌入式軟件處理器為核心來分別對圖像的采集、存儲,圖像處理,顯示等功能模塊進型結構設計,最后把處理數據通過網絡發送到接收端,從而完成了利用嵌入式系統和Internet技術的信息溝通。

- 關鍵字:

處理 理系 設計 圖像 數字 FPGA MB86S02 基于

- 本工程設計完全符合IP核設計的規范流程,而且完成了Verilog HDL建模、功能仿真、綜合、時序仿真等IP核設計的整個過程,電路功能正確。實際上,本系統在布局布線后,其系統的最高時鐘頻率可達80MHz。雖然使用浮點數會導致舍入誤差,但這種誤差很小,可以忽略。實踐證明,本工程利用流水線結構,方便地實現了高速、連續、大數據量浮點數的加法運算,而且設計結構合理,性能優異,可以應用在高速信號處理系統中。

- 關鍵字:

FPGA 流水線 浮點 加法器

- 介紹掃頻電路和DDS技術的原理,利用FPGA設計一個以DDS技術為基礎的掃頻信號源,給出用Verilog語言編程的實現方案和實現電路。并通過采用流水線技術提高了相位累加器的運算速度,通過改進ROM壓縮算法以減小存儲器的容量,完成了對整個系統的優化設計。運用QuartusⅡ軟件仿真驗證了程序設計的正確性,最終在硬件電路上實現了該掃頻信號源。

- 關鍵字:

FPGA 掃頻信號源

- Altera公司今天宣布了在即將推出的28nm FPGA中采用的創新技術:嵌入式HardCopy®模塊、部分重新配置新方法以及嵌入式28-Gbps收發器,這些技術將極大的提高下一代Altera® FPGA的密度和I/O性能,并進一步鞏固相對于ASIC和ASSP的競爭優勢。

快速增長的寬帶應用如高清晰(HD)視頻、云計算、網絡數據存儲和移動視頻等對基礎設備和最終用戶設備開發人員提出了新挑戰。他們怎樣才能夠迅速提高系統帶寬,同時滿足嚴格的功耗和成本要求呢?Altera開發了最新的創新

- 關鍵字:

Altera 28nm FPGA

- 意法半導體公布了截至2009年12月31日的第四季度和全年財務業績報告。

第四季度回顧

2009年第四季度意法半導體凈收入總計25.83億美元,包括意法半導體合賬的ST-Ericsson的銷售收入。凈收入環比增長13.6%,反映了意法半導體所有目標市場和所有地區市場的需求增長,特別是日本、大中國區和美洲區的需求增長更加強勁。除消費電子和工業以外的所有目標市場以及除日本以外的所有地區市場,凈收入均為同比增長,反映了半導體市場出現普遍復蘇跡象。

2009年第四季度意法半導體凈虧損收窄到7

- 關鍵字:

ST 消費電子 ASIC 汽車電子

- 基于FPGA設計的發電機組頻率測量計,系統在整體上采用光電耦合器的隔離方式,提高系統的抗干擾能力和穩定性。該系統具有線路簡單可靠、通用性強、穩定度高等優點,可廣泛應用于頻率電壓變換器、轉速繼電器。該設計的FPGA數字系統部分使用Verilog HDL語言,給出核心程序,并可以通過Verilog HDL語言的綜合工具進行相應硬件電路的生成,具有傳統邏輯設計方法所無法比擬的優越性。經過仿真后,驗證設計是成功的, 達到預期結果。同時這種方法設計的數字電子系統可移植性強、可更改性好。如果需要的頻率測量范圍需要擴

- 關鍵字:

FPGA 發電機組 測量計 頻率

asic-to-fpga介紹

您好,目前還沒有人創建詞條asic-to-fpga!

歡迎您創建該詞條,闡述對asic-to-fpga的理解,并與今后在此搜索asic-to-fpga的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473