cadence 文章 最新資訊

Cadence發(fā)布7納米工藝Virtuoso先進(jìn)工藝節(jié)點擴(kuò)展平臺

- 楷登電子(美國Cadence公司)今日正式發(fā)布針對7nm工藝的全新Virtuoso® 先進(jìn)工藝節(jié)點平臺。通過與采用7nm FinFET工藝的早期客戶展開緊密合作,Cadence成功完成了Virtuoso定制設(shè)計平臺的功能拓展,新平臺能幫助客戶管理由于先進(jìn)工藝所導(dǎo)致的更復(fù)雜的設(shè)計以及特殊的工藝效應(yīng)。新版Virtuoso先進(jìn)工藝平臺同樣支持所有主流FinFET先進(jìn)節(jié)點,性能已得到充分認(rèn)證;同時提高了7nm工藝的設(shè)計效率。 為了應(yīng)對7nm設(shè)計的眾多技術(shù)挑戰(zhàn),Virtuoso先進(jìn)工藝平臺提供豐富

- 關(guān)鍵字: Cadence Virtuoso

【E課堂】簡介:國內(nèi)流行的PCB設(shè)計軟件

- PCB設(shè)計軟件就是以電路原理圖為根據(jù),實現(xiàn)電路設(shè)計所需的功能。電路板的設(shè)計主要指版圖設(shè)計,需要考慮元器件和連線的整體布局,包括內(nèi)部電子元件的優(yōu)化布局;金屬連線和通孔的優(yōu)化布局;電磁防護(hù);散熱等各種因素。優(yōu)秀的PCB設(shè)計能夠達(dá)到良好的電路性能和散熱性能,節(jié)約生產(chǎn)成本。PCB設(shè)計需要借助計算機(jī)輔助設(shè)計(EDA)實現(xiàn)。下面介紹幾款國內(nèi)流行的PCB設(shè)計軟件。 Protel/Altium Designer 國內(nèi)低端設(shè)計的主流,簡單易學(xué),適合初學(xué)者。國內(nèi)使用protel還是有相當(dāng)有市場,畢竟小公司

- 關(guān)鍵字: PADS Cadence

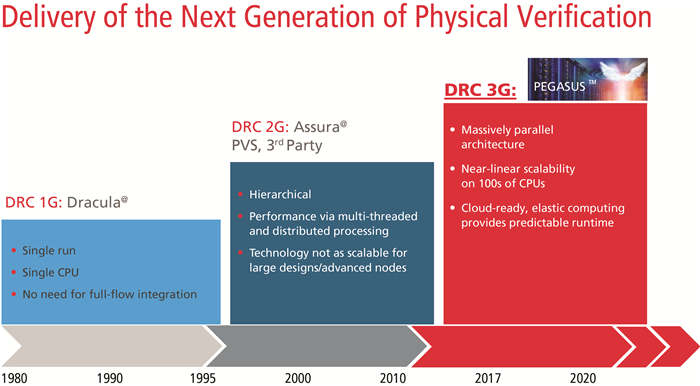

Cadence發(fā)布大規(guī)模并行物理簽核解決方案Pegasus驗證系統(tǒng)

- 楷登電子(美國 Cadence 公司)今日正式發(fā)布Pegasus?驗證系統(tǒng),該云計算(cloud-ready)大規(guī)模并行物理簽核解決方案將助工程師縮短先進(jìn)節(jié)點IC的上市時間。Pegasus?驗證系統(tǒng)解決方案是全流程Cadence數(shù)字設(shè)計與簽核套件的新成員,可擴(kuò)展至數(shù)百CPU,設(shè)計規(guī)則檢查(DRC)性能最高可提升10倍,周轉(zhuǎn)時間較上一代Cadence? 解決方案由數(shù)日降至數(shù)小時。如需了解Pegasus驗證系統(tǒng)的詳細(xì)內(nèi)容,請參訪www.cadence.com/go/pegas

- 關(guān)鍵字: Cadence Pegasus

Cadence獲得TSMC 7nm工藝技術(shù)認(rèn)證

- 楷登電子(美國 Cadence 公司,NASDAQ: CDNS)今日正式宣布與臺灣積體電路制造股份有限公司(TSMC)取得的多項合作成果,進(jìn)一步強(qiáng)化面向移動應(yīng)用與高性能計算(HPC)平臺的7nm FinFET工藝創(chuàng)新。Cadence? 數(shù)字簽核與定制/模擬電路仿真工具獲得TSMC 7nm工藝 v1.0設(shè)計規(guī)則手冊(DRM)認(rèn)證及SPICE認(rèn)證。合作期間,Cadence開發(fā)了包括多種解決方案的全新工藝設(shè)計包(PDK),進(jìn)一步實現(xiàn)功耗、

- 關(guān)鍵字: Cadence 7nm

Cadence與TSMC合作12FFC工藝技術(shù),驅(qū)動IC設(shè)計創(chuàng)新

- 楷登電子(美國 Cadence 公司)今日正式公布其與臺灣積體電路制造股份有限公司(TSMC)全新12nm FinFET緊湊型(12FFC)工藝技術(shù)開發(fā)的合作內(nèi)容。憑借Cadence? 數(shù)字與Signoff解決方案、定制/模擬電路仿真解決方案及IP,系統(tǒng)級芯片(SoC)設(shè)計師可以利用12FFC工藝開發(fā)正在快速發(fā)展的中端移動和高端消費電子應(yīng)用。上述應(yīng)用對PPA性能(功耗、性能和面積)的要求更高,為此,Cadence正與12FFC工藝的早期客戶開展緊密合作。 Ca

- 關(guān)鍵字: Cadence TSMC

Cadence推出用于早期軟件開發(fā)的FPGA原型驗證平臺Protium S1

- 楷登電子(美國?Cadence?公司)今日發(fā)布全新基于FPGA的Protium??S1原型驗證平臺。借由創(chuàng)新的實現(xiàn)算法,平臺可顯著提高工程生產(chǎn)效率。Protium?S1與Cadence??Palladium??Z1企業(yè)級仿真平臺前端一致,初始設(shè)計啟動速度較傳統(tǒng)FPGA原型平臺提升80%。Protium?S1采用Xilinx??Virtex??UltraScale??FPGA技術(shù),設(shè)計容量比上一代平臺提升

- 關(guān)鍵字: Cadence Protium S1

Cadence發(fā)布業(yè)界首款已通過產(chǎn)品流片驗證的Xcelium并行仿真平臺

- 楷登電子(美國 Cadence 公司)今日發(fā)布業(yè)界首款已通過產(chǎn)品流片的第三代并行仿真平臺Xcelium? 。基于多核并行運算技術(shù),Xcelium? 可以顯著縮短片上系統(tǒng)(SoC)面市時間。較Cadence上一代仿真平臺,Xcelium? 單核版本性能平均可提高2倍,多核版本性能平均可提高5倍以上。Cadence? Xcelium仿真平臺已經(jīng)在移動、圖像、服務(wù)器、消費電子、物聯(lián)網(wǎng)(IoT)和汽車等多個領(lǐng)域的早期用戶中得到了成功應(yīng)用,并通過產(chǎn)品流

- 關(guān)鍵字: Cadence Xcelium

Cadence與西安電子科技大學(xué)攜手共建集成電路設(shè)計培訓(xùn)中心

- 楷登電子(美國 Cadence 公司)與西安電子科技大學(xué)共同宣布,Cadence將與西安電子科技大學(xué)攜手共建集成電路設(shè)計培訓(xùn)中心(下稱“聯(lián)合培訓(xùn)中心”),并在西安電子科技大學(xué)隆重舉行了西電、CSIP、Cadence戰(zhàn)略合作會議暨聯(lián)合培訓(xùn)中心揭牌儀式。西安電子科技大學(xué)副校長李建東和Cadence全球副總裁兼亞太區(qū)總裁石豐瑜先生,與陜西省工業(yè)和信息化廳電子信息處處長高翔和工業(yè)和信息化部軟件與集成電路促進(jìn)中心集成電路處負(fù)責(zé)人霍雨濤共同為聯(lián)合培訓(xùn)中心進(jìn)行揭牌。在揭牌儀式之后,西安電子科

- 關(guān)鍵字: Cadence 集成電路

加強(qiáng)產(chǎn)業(yè)協(xié)作,布局生態(tài)創(chuàng)新 ARM宣布在中國重慶多項戰(zhàn)略合作

- ARM?今日宣布加強(qiáng)在中國的戰(zhàn)略部署,與重慶市政府、重慶仙桃數(shù)據(jù)谷達(dá)成多項協(xié)議,建立合作計劃,共同推進(jìn)重慶仙桃數(shù)據(jù)谷電子產(chǎn)業(yè)創(chuàng)新生態(tài)圈建設(shè)。當(dāng)日,雙方共同為位于仙桃數(shù)據(jù)谷的ARM生態(tài)產(chǎn)業(yè)園揭幕;并宣布成立重慶地區(qū)ARM生態(tài)集成電路人才培養(yǎng)與產(chǎn)學(xué)研協(xié)同創(chuàng)新聯(lián)盟,建立重慶ARM生態(tài)產(chǎn)業(yè)技術(shù)人才實訓(xùn)中心;此外,由ARM和中科創(chuàng)達(dá)共同投資的創(chuàng)業(yè)加速器安創(chuàng)空間宣布其重慶公司開業(yè),正式落戶重慶仙桃數(shù)據(jù)谷ARM生態(tài)產(chǎn)業(yè)園。 A

- 關(guān)鍵字: ARM Cadence

Cadence發(fā)布完整數(shù)字與簽核參考流程用于Imagination Technologies公司PowerVR Series7 GPU

- Cadence設(shè)計系統(tǒng)公司今日宣布,正式交付完整的數(shù)字與簽核參考流程,用于Imagination Technologies (IMG.L)公司PowerVR Series7圖形處理單元(GPU)。采用此高度集成的Cadence® 參考流程,550萬實例的完整合成與設(shè)計實現(xiàn)可在2.5天完成。對比上一代Cadence設(shè)計流程,產(chǎn)品開發(fā)設(shè)計時間縮短1倍以上。同時,采納新參考流程后,芯片面積平均縮小3%,Imagination最復(fù)雜的組塊面積可縮小達(dá)7%。 此參考流程操作簡單,僅需單次執(zhí)行;同時

- 關(guān)鍵字: Cadence GPU

cadence介紹

EDA仿真軟件Cadence

--------------------------------------------------------------------------------

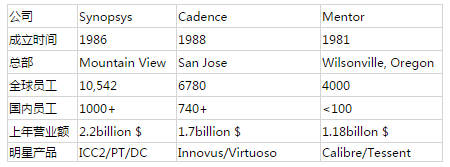

Cadence Design Systems Inc.是全球最大的電子設(shè)計技術(shù)(Electronic Design Technologies)、程序方案服務(wù)和設(shè)計服務(wù)供應(yīng)商。其解決方案旨在提升和監(jiān)控半導(dǎo) [ 查看詳細(xì) ]

相關(guān)主題

熱門主題

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司