- 1 引言

大多數(shù)非FPGA類型的、高密度IC(如CPU)對(duì)去耦電容都有非常明確的要求。由于這些器件僅為執(zhí)行特定的任務(wù)而設(shè)計(jì),所以其電源電流需求是固定的,僅在一定范圍內(nèi)有所波動(dòng)。 然而,F(xiàn)PGA不具備這種

- 關(guān)鍵字:

FPGA 分析

- 借助物理綜合提高FPGA設(shè)計(jì)效能,隨著FPGA密度的增加,系統(tǒng)設(shè)計(jì)人員能夠開發(fā)規(guī)模更大、更復(fù)雜的設(shè)計(jì),從而將密度優(yōu)勢(shì)發(fā)揮到最大。這些大規(guī)模設(shè)計(jì)基于這樣的設(shè)計(jì)需求――需要在無線通道卡或者線路卡等現(xiàn)有應(yīng)用中加入新功能,或者通過把兩種芯片功能合

- 關(guān)鍵字:

設(shè)計(jì) 效能 FPGA 提高 物理 綜合 借助

- 隨著電力電子技術(shù)的迅猛發(fā)展,電力系統(tǒng)中非線性負(fù)荷大量增加,各種非線性和時(shí)變性電子裝置如逆變器、整流器及各種開關(guān)電源的應(yīng)用越來越廣泛,由此帶來的諧波和無功問題日益嚴(yán)重。采用電力濾波裝置就近吸收非線性

- 關(guān)鍵字:

濾波器 研究 電力 有源 DSP 基于

-

1 引 言由于雷達(dá)所處的環(huán)境的復(fù)雜性,除了地物、云雨、鳥群等干擾外,還可能來自臨近的雷達(dá)異步干擾、電臺(tái)干擾等。所有的干擾,經(jīng)過接收機(jī)進(jìn)入信號(hào)處理機(jī),雖然經(jīng)過了中頻信號(hào)的處理,但還可能有殘余。因

- 關(guān)鍵字:

FPGA 雷達(dá)視頻 積累 算法

- 0引言傳統(tǒng)氣體壓力測(cè)量儀器的傳感器部分與數(shù)據(jù)采集系統(tǒng)是分離的,抗干擾的能力較差,并且通常被測(cè)對(duì)...

- 關(guān)鍵字:

FPGA 智能壓力傳感器系統(tǒng)

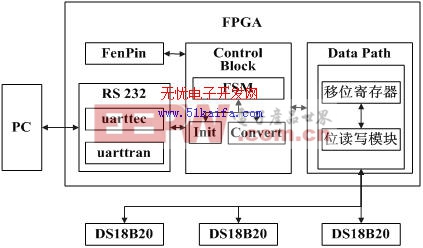

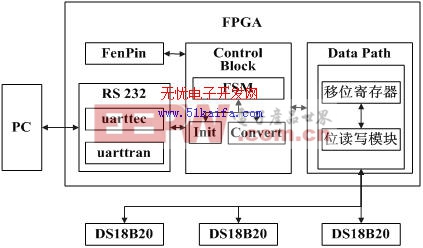

- 摘要:溫度的監(jiān)測(cè)與控制,對(duì)于工業(yè)生產(chǎn)的發(fā)展有著非常重要的意義。分析并設(shè)計(jì)了基于數(shù)字化一線總線技術(shù)的智能溫度測(cè)控系統(tǒng)。本系統(tǒng)采用FPGA實(shí)現(xiàn)一個(gè)溫度采集控制器,用于傳感器和上位機(jī)的連接,并采用微軟公司的Visu

- 關(guān)鍵字:

一線總線 異步通訊 FPGA MSCOMM

- 摘 要 介紹了采用FPGA和DSP直接控制硬盤進(jìn)行數(shù)據(jù)存儲(chǔ)的方法,并采用一片F(xiàn)IFO作為數(shù)據(jù)緩存,能夠滿足80Khz數(shù)據(jù)采樣率系統(tǒng)的存盤要求。 關(guān)鍵詞 FPGA;DSP;硬盤;數(shù)據(jù)存儲(chǔ) 1 引言 數(shù)據(jù)存儲(chǔ)是數(shù)據(jù)采集過程中

- 關(guān)鍵字:

FPGA DSP 直接控制 硬盤

- DSP和小波變換在配電網(wǎng)接地選線中的應(yīng)用, 摘要:本文應(yīng)用小波包良好的頻域分頻特性,以適當(dāng)頻率帶寬對(duì)配電網(wǎng)發(fā)生單相接地故障后暫態(tài)電氣量進(jìn)行分解,得到其在不同頻段下的輸出。對(duì)于中性點(diǎn)接地方式不同的配電網(wǎng),按照能量的觀點(diǎn),選擇不同的頻段,利用波形

- 關(guān)鍵字:

接地 應(yīng)用 電網(wǎng) 變換 小波 DSP

- 隨著系統(tǒng)級(jí)芯片技術(shù)的出現(xiàn),設(shè)計(jì)規(guī)模正變得越來越大,因而變得非常復(fù)雜,同時(shí)上市時(shí)間也變得更加苛刻。通常RTL已經(jīng)不足以擔(dān)當(dāng)這一新的角色。上述這些因素正驅(qū)使設(shè)計(jì)師開發(fā)新的方法學(xué),用于復(fù)雜IP(硬件和軟件)以及復(fù)雜

- 關(guān)鍵字:

SystemC FPGA TLM IP開發(fā)

- 在DSP處理器上并行實(shí)現(xiàn)ATR算法, 自動(dòng)目標(biāo)識(shí)別(ATR)算法通常包括自動(dòng)地對(duì)目標(biāo)進(jìn)行檢測(cè)、跟蹤、識(shí)別和選擇攻擊點(diǎn)等算法。戰(zhàn)場環(huán)境的復(fù)雜性和目標(biāo)類型的不斷增長使ATR算法的運(yùn)算量越來越大,因此ATR算法對(duì)微處理器的處理能力提出了更高的要求。由于

- 關(guān)鍵字:

ATR 算法 實(shí)現(xiàn) 并行 處理器 DSP

- 為解決單片F(xiàn)PGA無法滿足復(fù)雜SoC原型驗(yàn)證所需邏輯資源的問題,設(shè)計(jì)了一種可層疊組合式超大規(guī)模SoC驗(yàn)證系統(tǒng)。該系統(tǒng)采用了模塊化設(shè)計(jì),通過互補(bǔ)連接器和JTAG控制電路,支持最多5個(gè)原型模塊的層疊組合,最多可提供2 500萬門邏輯資源。經(jīng)本系統(tǒng)驗(yàn)證的地面數(shù)字電視多媒體廣播基帶調(diào)制芯片(BHDTMBT1006)已成功流片。

- 關(guān)鍵字:

FPGA SoC 層疊 組合式

- 如何實(shí)現(xiàn)高性能的DSP處理, 應(yīng)用開發(fā)通常開始于在個(gè)人電腦或工作站編寫的C原型代碼,然后將代碼移植到嵌入式處理器中,并加以優(yōu)化。本系列文章則將這種層面的優(yōu)化在系統(tǒng)級(jí)擴(kuò)展到包括以下三方面的技術(shù):內(nèi)存管理,DMA管理,系統(tǒng)中斷管理。這些

- 關(guān)鍵字:

處理 DSP 高性能 實(shí)現(xiàn) 如何

- 基于DSP和DDS的三維感應(yīng)測(cè)井高頻信號(hào)源實(shí)現(xiàn), 引言 高頻信號(hào)源設(shè)計(jì)是三維感應(yīng)測(cè)井的重要組成部分。三維感應(yīng)測(cè)井的原理是利用激勵(lì)信號(hào)源通過三個(gè)正交的發(fā)射線圈向外發(fā)射高頻信號(hào),再通過多組三個(gè)正交的接收線圈,得到多組磁場分量,從而準(zhǔn)確測(cè)量地層各向異性

- 關(guān)鍵字:

高頻 信號(hào)源 實(shí)現(xiàn) 測(cè)井 感應(yīng) DSP DDS 三維 基于

- 引言 隨著計(jì)算機(jī)的普及和信息處理技術(shù)的廣泛應(yīng)用,不間斷電源UPS在關(guān)鍵負(fù)載連接至公共電網(wǎng)方面扮演著重要角色。它們旨在為處于任何正常或異常實(shí)用電源條件下的負(fù)載提供清潔、持續(xù)的電源。德州儀器(TI)TMS320F28

- 關(guān)鍵字:

電源 控制系統(tǒng) 研究 間斷 UPS DSP 在線式 基于

fpga+dsp介紹

您好,目前還沒有人創(chuàng)建詞條fpga+dsp!

歡迎您創(chuàng)建該詞條,闡述對(duì)fpga+dsp的理解,并與今后在此搜索fpga+dsp的朋友們分享。

創(chuàng)建詞條

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473