fpga+dsp 文章 最新資訊

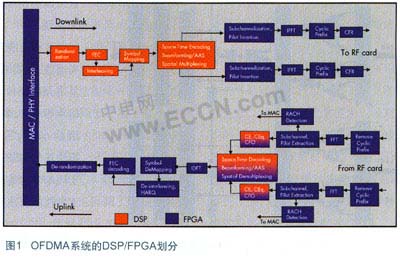

MIMO-OFDMA無線基站的DSP-FPGA系統(tǒng)劃分

- 引言 無線運營商通過提供增強數(shù)據(jù)服務(wù)來提高單位用戶平均收益(ARPU),這同時推動了對寬帶的需求,導(dǎo)致對數(shù)據(jù)速率的要求越來越高。而且,為用戶提供各種應(yīng)用體驗的要求也促使底層網(wǎng)絡(luò)體系結(jié)構(gòu)進行變革。窄帶2G GSM、IS-95系統(tǒng)等以語音為中心的技術(shù)已經(jīng)發(fā)展到了基于WCDMA的HSDPA和HSUPA系統(tǒng),峰值數(shù)據(jù)速率達到了10Mbps。今后的3GPP長期發(fā)展規(guī)范采用了多輸入多輸出(MIMO)等復(fù)雜的信號處理技術(shù),以及正交頻分復(fù)用接入(OFDMA)和多載波碼分復(fù)用接入(MC-CDMA)等新的射頻技術(shù),這些

- 關(guān)鍵字: MIMO WiMAX LTE 3G FPGA

TI &SEED達芬奇技術(shù)培訓(xùn)在深圳大學(xué)圓滿結(jié)束

- 憑借合眾達多年TI DSP開發(fā)經(jīng)驗積累以及在DaVinci平臺軟硬件研究,TI正式官方授權(quán)SEED成為國內(nèi)TI DaVinci培訓(xùn)第三方并承辦國內(nèi)達芬奇技術(shù)培訓(xùn)活動,合眾達總工程師成為TI指定DaVinci培訓(xùn)高級工程師。 2008年7月15~18日,首場TI&SEED “DM644x DaVinciTM 4-day Workshop” 培訓(xùn)在深圳大學(xué)-TI DSPs 聯(lián)合實驗室圓滿結(jié)束,硬件平臺采用合眾達公司達芬奇平臺:SEED-DVS6446板卡,學(xué)員人數(shù)達到

- 關(guān)鍵字: 合眾達 TI DSP 培訓(xùn)

TI推出業(yè)界最低功耗浮點DSP---TMS320C674X

- TI最新推出業(yè)界內(nèi)最低功耗的浮點DSP---TMS320C674X,性能高,非常適合工業(yè)現(xiàn)場應(yīng)用: ·業(yè)界最低的功耗和豐富的外設(shè)接口,使其具有良好的便攜性和有線應(yīng)用 ·精度高,動態(tài)范圍寬,24/32位精確浮點型DSP核心 ·通過高性能一體化和低定價,能夠有效降低系統(tǒng)成本,不到10美元@ 100u數(shù)量 ·具有20倍低于標準備用電源和1 / 3功率消耗的性能 c674x DSP應(yīng)用: 音樂效果

- 關(guān)鍵字: TI DSP TMS320C674X 便攜

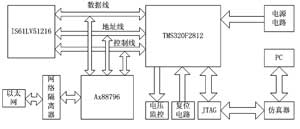

基于TMS320F2812的快速以太網(wǎng)通信系統(tǒng)平臺

- 引言 隨著Internet應(yīng)用的日益普及,信息共享程度的不斷提高。嵌入式設(shè)備的數(shù)字化和網(wǎng)絡(luò)化已經(jīng)成為必然趨勢,目前市場上的主流嵌入式操作系統(tǒng)都包含了TCP/IP網(wǎng)絡(luò)協(xié)議棧。這些商品化的TCP/IP協(xié)議棧運行可靠、性能也非常好,但是價格較高,降低了市場競爭力。因此,開發(fā)自主知識產(chǎn)權(quán)的TCP/IP協(xié)議棧的要求變的日益迫切而有意義。 本文的研究目標是建立一個DSP系統(tǒng)的網(wǎng)絡(luò)通信平臺,實現(xiàn)DSP系統(tǒng)與網(wǎng)絡(luò)中其他通信設(shè)備的高速數(shù)據(jù)傳輸。雖然選擇了TI公司的TMS320F2812 DSP,但是本文提出

- 關(guān)鍵字: 網(wǎng)絡(luò)通信 嵌入式 TCP/IP DSP

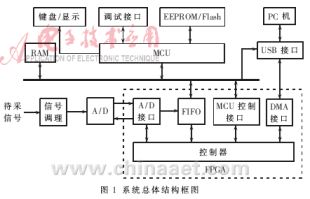

基于USB2.0與FPGA技術(shù)的高速數(shù)據(jù)采集系統(tǒng)的設(shè)計

- 近年來筆記本電腦迅速普及和更新,其中大部分已經(jīng)不配置RS232接口,而USB接口已成為今后一段時間PC機與外設(shè)接口的主流。本采集系統(tǒng)的設(shè)計構(gòu)建了一個基于USB接口的多功能通用數(shù)據(jù)采集、傳輸平臺,將嵌入式系統(tǒng)的實時性、靈活性和PC機強大的數(shù)據(jù)存儲、處理、顯示功能結(jié)合起來。該采集系統(tǒng)在智能儀器儀表、測控系統(tǒng)、工控系統(tǒng)等領(lǐng)域有廣闊的應(yīng)用前景。 1 系統(tǒng)總體結(jié)構(gòu)設(shè)計 1.1 系統(tǒng)總體結(jié)構(gòu) 系統(tǒng)總體結(jié)構(gòu)框圖如圖1所示,系統(tǒng)包括:單片機與USB接口模塊、FPGA模塊、信號調(diào)理及A/D模塊。其中,單片

- 關(guān)鍵字: 單片機 USB FPGA A/D

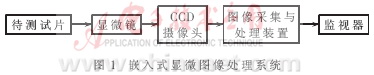

基于DSP的嵌入式顯微圖像處理系統(tǒng)的設(shè)計

- 顯微圖像處理是數(shù)字圖像處理的一個重要研究領(lǐng)域,隨著其技術(shù)的不斷發(fā)展,已經(jīng)在材料、生物、醫(yī)學(xué)等領(lǐng)域得到了廣泛應(yīng)用[1][2]。目前的顯微圖像處理通常利用圖像采集系統(tǒng)將顯微圖像采集到計算機中再進行圖像處理,這樣,雖然運算速度高,但體積龐大、不便于攜帶,有一定的局限性。因此,采用數(shù)字圖像處理技術(shù)和DSP技術(shù)實現(xiàn)顆粒顯微圖像的高效、快速、全面的統(tǒng)計與測量,具有重要的實用價值和廣闊的應(yīng)用前景。 本文提出并設(shè)計了一種基于DSP和FPGA的嵌入式顯微圖像采集處理系統(tǒng),如圖1所

- 關(guān)鍵字: DSP 圖像處理 顯微 FPGA

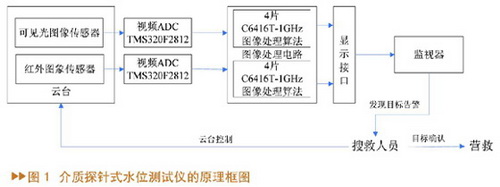

用于海洋搜救的多片DSP圖像處理識別系統(tǒng)的實現(xiàn)

- 引言 海上搜救服務(wù)是國家應(yīng)急救援體系的重要組成部分,也是國家經(jīng)濟發(fā)展的重要保障。采用先進的搜索系統(tǒng)是提高搜救行動有效性的重要手段之一。通常情況下搜索系統(tǒng)采用雷達或者光電成像系統(tǒng),因為光圖像傳感器具有很高的分辨率,在能見度理想的情況下,觀測距離可達20~40km,但它的缺點就是在較大程度上依賴良好的天氣及日照條件。而紅外圖像傳感器具有穿透煙、霧、霾、雪等能力,可彌補這一不足,因此采用紅外、可見光成像和DSP圖像處理系統(tǒng)構(gòu)成的光電搜索系統(tǒng)。 根據(jù)海洋搜救的性質(zhì),該系統(tǒng)應(yīng)具備以下基本能力: &mi

- 關(guān)鍵字: DSP 圖像處理 VGA AD轉(zhuǎn)換

GE Fanuc智能設(shè)備推出首個加固XMCV5夾層卡

- 針對數(shù)字信號處理應(yīng)用而設(shè)計;可應(yīng)用于最惡劣的環(huán)境當(dāng)中 * Xilinx Virtex FPGA 處理器 * 5種加固選項 * 靈活配置選項 * 兼容 VITA-42.0、VITA 42.2 和VITA 42.3 GE Fanuc 智能設(shè)備近日發(fā)布支持Xilinx Virtex-5 FPGA 的XMCV5夾層卡,以滿足軍事和航空領(lǐng)域客戶日益增長的對FPGA技術(shù)的需求。我們設(shè)計的XMCV5應(yīng)用范圍十分廣泛,在數(shù)字信號(DSP)處理應(yīng)用方面,可應(yīng)用于地面移動通信、飛機固定和旋

- 關(guān)鍵字: FPGA 數(shù)字信號處理 GE Fanuc 夾層卡

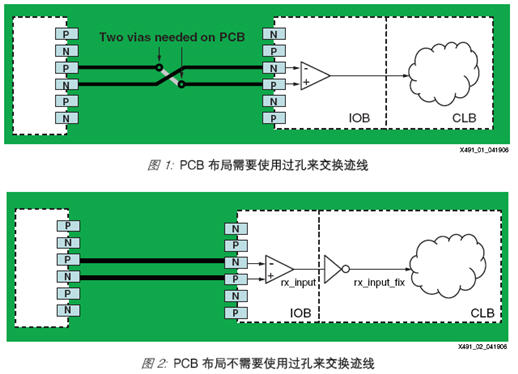

Spartan-3 FPGA系列中高效PCB布局的LVDS信號倒相

- 提要 在比較簡單的未大量使用過孔的四層或六層 PCB 上,可能很難對 LVDS 或 LVPECL 這類差分信號布線。其原因是,驅(qū)動器上的正極引腳必須驅(qū)動接收器上的相應(yīng)正極引腳,而負極引腳則必須驅(qū)動接收器的負極引腳。有時跡線以錯誤的方向結(jié)束,這實際上是向電路中添加了一個倒相器。本應(yīng)用指南說明 Spartan?- 3 FPGA 系列如何僅通過在接收器數(shù)據(jù)通路中加入一個倒相器即可避免大量使用過孔,并且在不要求 PCB 重新設(shè)計的情況下即可解決意外的 PCB 跡線交換問題。這項技術(shù)同樣適用于將 FPGA

- 關(guān)鍵字: PCB LVDS 倒相器 FPGA SDR

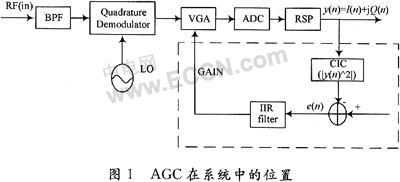

3G系統(tǒng)中AGC的FPGA設(shè)計實現(xiàn)

- 1 引 言 大多數(shù)接收機必須處理動態(tài)范圍很大的信號,這需要進行增益調(diào)整,以防止過載或某級產(chǎn)生互調(diào),調(diào)整解調(diào)器的工作以優(yōu)化工作。在現(xiàn)代無線電接收裝置中。可變增益放大器是電控的,并且當(dāng)接收機中使用衰減器時,他們通常都是由可變電壓控制的連續(xù)衰減器。控制應(yīng)該是平滑的并且與輸入的信號能量通常成對數(shù)關(guān)系(線性分貝)。在大多數(shù)情況下,由于衰落,AGC通常用來測量輸入解調(diào)器的信號電平,并且通過反饋控制電路把信號電平控制在要求的范同內(nèi)。 2 系統(tǒng)總體設(shè)計 在本設(shè)計中,前端TD_SCDM

- 關(guān)鍵字: TD_SCDMA AGC FPGA RSP IIR

利用FPGA實現(xiàn)工業(yè)以太網(wǎng)交換機設(shè)計優(yōu)化

- 利用FPGA實現(xiàn)工業(yè)以太網(wǎng)交換機設(shè)計優(yōu)化,工業(yè)以太網(wǎng)技術(shù)一直在進步,并越來越普及,而設(shè)計師面臨著對高性價比工業(yè)交換機日益強勁的需求。基于ASIC和ASSP的交換機因其架構(gòu)固定,所以實際上沒有余地定制出新的系統(tǒng)特性。為了增加特性設(shè)計一般要推倒重來,此舉會導(dǎo)致額外的設(shè)計時間和成本支出。但如上所述的支持IEEE 1588交換機的FPGA設(shè)計可節(jié)省6到9個月的工程時間,并提供給設(shè)計師夢寐以求的靈活性,幫助他們實現(xiàn)精確定時協(xié)議(PTP)、 支持多個工業(yè)以太網(wǎng)標準、額外的標準接口或者其它可能的定制特性。

- 關(guān)鍵字: 交換機 設(shè)計 優(yōu)化 以太網(wǎng) 工業(yè) FPGA 實現(xiàn) 利用

ADI與中國合作伙伴共推Blackfin開發(fā)工具 營建本地DSP生態(tài)環(huán)境

- 亞德諾半導(dǎo)體公司(Analog Devices, Inc., ADI)與中國區(qū)合作伙伴共同宣布可向市場提供全系列的Blackfin本地開發(fā)工具。這些本地開發(fā)工具包括仿真器、開發(fā)板和軟件模塊,針對的處理器范圍包括從BF531到最新的BF52x和BF54x的全系列Blackfin。 作為世界領(lǐng)先的通用DSP處理器提供商,ADI公司一直致力于向客戶提供技術(shù)先進及商業(yè)用途廣泛的DSP處理器芯片和方案,同時也深刻理解DSP應(yīng)用開發(fā)的各個環(huán)節(jié),了解開發(fā)工具對于客戶的重要價值。除了自己設(shè)計制造完善的開發(fā)工具,

- 關(guān)鍵字: ADI DSP Blackfin 開發(fā)工具

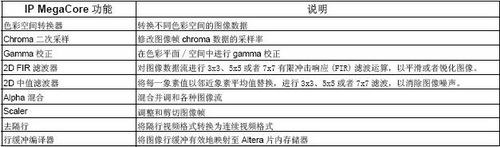

在高清晰LCD HDTV中使用Cyclone III FPGA

- 引言 當(dāng)今的液晶顯示(LCD) 技術(shù)在高清晰電視(HDTV) 領(lǐng)域得到了廣泛應(yīng)用,其挑戰(zhàn)在于如何獲得更高的分辨率,實現(xiàn)更快的數(shù)據(jù)速率。提高數(shù)據(jù)速率需要專業(yè)圖像處理算法來支持快速移動的視頻。業(yè)界遇到的主要問題是:怎樣實現(xiàn)這些算法,率先將產(chǎn)品推向市場,并且能夠控制好產(chǎn)品功耗? 為解決這一問題,當(dāng)硬件平臺和不同尺寸的LCD 顯示屏連接時,設(shè)計人員需要確定怎樣重新配置圖像處理算法。面積較大的LCD 顯示屏需要更快的數(shù)據(jù)速率,因此,難點在于怎樣根據(jù)顯示屏大小來調(diào)整數(shù)據(jù)速率。 采用新的低成本Cy

- 關(guān)鍵字: FPGA Cyclone III LCD HDTV

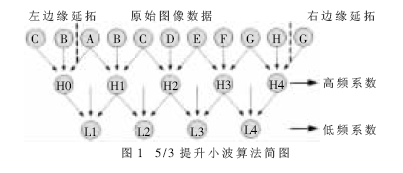

5/3提升小波在DM642上的實現(xiàn)與優(yōu)化

- 提升小波變換不僅具有傳統(tǒng)小波多分辨率的優(yōu)點,而且簡化了運算,便于硬件實現(xiàn),因此在數(shù)字圖像編碼中得到廣泛應(yīng)用。在新的圖像壓縮標準JPEG2000中,采用9/7、5/3提升小波變換作為編碼算法,其中5/3小波變換是一種可逆的整數(shù)變換,可以實現(xiàn)無損或有損的圖像壓縮。在通用的DSP芯片上實現(xiàn)該算法具有很好的可擴展性、可升級性與易維護性。用這種方式靈活性強,完全能滿足各種處理需求。 1提升算法 提升算法[1]是由Sweldens等在Mallat算法的基礎(chǔ)上提出的,也稱為第二代小波變換。與Mallat算法

- 關(guān)鍵字: DSP 小波變換 數(shù)字圖像編碼 5/3

fpga+dsp介紹

您好,目前還沒有人創(chuàng)建詞條fpga+dsp!

歡迎您創(chuàng)建該詞條,闡述對fpga+dsp的理解,并與今后在此搜索fpga+dsp的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對fpga+dsp的理解,并與今后在此搜索fpga+dsp的朋友們分享。 創(chuàng)建詞條

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司