fpga+dsp 文章 最新資訊

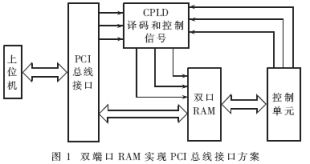

用雙端口RAM實現(xiàn)與PCI總線接口的數(shù)據(jù)通訊

- 采用雙端口RAM實現(xiàn)DSP與PCI總線芯片之間的數(shù)據(jù)交換接口電路。 提出了一種使用CPLD解決雙端口RAM地址譯碼和PCI接口芯片局部總線仲裁的的硬件設計方案,并給出了PCI總線接口芯片寄存器配置實例,介紹了軟件包WinDriver開發(fā)設備驅動程序的具體過程。 隨著計算機技術的不斷發(fā)展,為滿足外設間以及外設與主機間的高速數(shù)據(jù)傳輸,Intel公司于1991年提出了PCI總線概念。PCI總線是一種能為主CPU及外設提供高性能數(shù)據(jù)通訊的總線,其局部總線在33MHz總線時鐘、32位數(shù)據(jù)通路時,數(shù)據(jù)

- 關鍵字: RAM DSP PCI總線 CPLD 數(shù)據(jù)通訊

基于DSP和USB的高速數(shù)據(jù)采集與處理系統(tǒng)設計

- 介紹了一種基于DSP與USB的高速數(shù)據(jù)采集與處理系統(tǒng),包括整個系統(tǒng)的硬件設計與軟件設計。DSP控制整個系統(tǒng)完成CCD信號采集并進行小波變換去噪處理,F(xiàn)PGA協(xié)同DSP實現(xiàn)整個系統(tǒng)的地址譯碼和邏輯控制。主機應用程序通過USB完成與DSP的數(shù)據(jù)通信,實現(xiàn)整個采集的控制和數(shù)據(jù)顯示。這種高速的數(shù)據(jù)采集與處理系統(tǒng),可廣泛地應用于各種智能儀表、自動化控制設備中,有著非常好的市場應用前景。

- 關鍵字: 處理 理系 設計 數(shù)據(jù)采集 高速 DSP USB 基于

一種基于分層級連DSP陣列技術的電子浮標設計

- 和其他水下目標探測裝備(如艇殼聲納、拖線陣聲納等)相比,電子浮標由于沒有本艦噪聲的影響,對水下目標的探測靈敏度高;此外它可通過飛機布放和回收,具有搜索面積大、偵察效率高、使用方便等優(yōu)點,已成為偵察、反潛領域的重要裝備。而將多個浮標組成網(wǎng)絡,就可對大范圍海域進行監(jiān)視。目前,作為數(shù)字化海洋的重要組成部分,電子浮標已成 世界海洋國家不惜巨資進行開發(fā)的水下目標監(jiān)測裝備。 本文介紹了一種基于分層級連DSP陣列技術的電子浮標設計方案,該方案通過微弱信號檢測技術來提取水下目標的聲信號;通過差分GPS技術來給浮

- 關鍵字: DSP 電子浮標 GPS 無線通訊 檢測

Altera發(fā)布業(yè)界首款40-nm FPGA和HardCopy ASIC

- ? 為幫助設計人員提高集成度,進一步創(chuàng)新,Altera公司今天發(fā)布了業(yè)界的首款40-nm FPGA和HardCopy? ASIC。Stratix? IV FPGA和HardCopy IV ASIC都提供收發(fā)器,在密度、性能和低功耗上遙遙領先。Stratix IV系列有680K邏輯單元(LE),比Altera的Stratix III系列高2倍,是目前市場上密度最大的FPGA。HardCopy IV ASIC系列在密度上和Stratix IV器件等價,具有1330萬邏輯門。Alte

- 關鍵字: Altera 40-nm FPGA ASIC

德州儀器:2020年半導體發(fā)展趨勢

- 德州儀器(TI)開發(fā)商大會(TI Developer Conference)5月26日起在中國召開。本次大會依次在深圳、上海和北京舉辦,在深圳的首場報告中,TI 首席科學家方進 (Gene Frantz) 和與會者分享了2020年半導體產(chǎn)業(yè)發(fā)展趨勢,闡述科技將如何改變未來生活,并展示了一系列極富創(chuàng)意和前瞻性的嶄新思想,將大眾帶入2020年的未來科技世界。這是半導體科技界讓人充滿期望的一次盛宴。 方進指出,隨著對視訊影像、車用電子、通訊設備、工業(yè)應用及醫(yī)療電子等相關應用的需求提升,全球 DS

- 關鍵字: 德州儀器 DSP 集成電路 低功耗節(jié)能 SiP 機器人 醫(yī)療電子

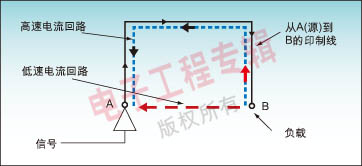

如何避免在DSP系統(tǒng)中出現(xiàn)噪聲和EMI問題

- ?? 在任何高速數(shù)字電路設計中,處理噪聲和電磁干擾(EMI)都是一個必然的挑戰(zhàn)。處理音視頻和通信信號的數(shù)字信號處理(DSP)系統(tǒng)特別容易遭受這些干擾,設計時應該及早搞清楚潛在的噪聲和干擾源,并及早采取措施將這些干擾降到最小。良好的規(guī)劃將減少調試階段中的大量時間和工作的反復,從而會節(jié)省總的設計時間和成本。 如今,最快的DSP的內部時鐘速率高達數(shù)千兆赫,而發(fā)射和接收信號的頻率高達幾百兆赫。這些高速開關信號將會產(chǎn)生大量的噪聲和干擾,將影響系統(tǒng)性能并產(chǎn)生電平很高的EMI。而DSP系統(tǒng)也

- 關鍵字: DSP 視頻系統(tǒng) 噪聲 電磁干擾 EMI

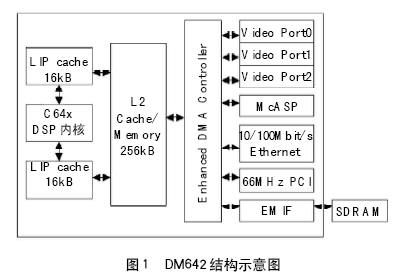

多媒體處理器DM642及其在視頻監(jiān)控中的應用

- 引 言 視頻監(jiān)控系統(tǒng)的設計方案有很多種,但是市場產(chǎn)品的主流一般選擇兩種方案:一是基于CPU和專用的視頻編解碼ASIC芯片。該方案選擇以ARM為核心的CPU和專用媒體處理芯片搭建。優(yōu)點是開發(fā)時間相對較短,但由于采用ASIC,靈活性較差,產(chǎn)品一旦定型,很難更改。二是采用面向媒體處理的專用DSP。其開發(fā)時間不長,優(yōu)點是由于算法是軟件代碼,所以可以不斷對產(chǎn)品性能進行升級,重復開發(fā)成本較低。由全球最大的DSP制造商德州儀器(TI)推出的TMS320DM642(以下簡稱DM642)作為一款高性價比、專用于多

- 關鍵字: 多媒體 處理器 視頻監(jiān)控 ASIC CPU DSP CCS DM642

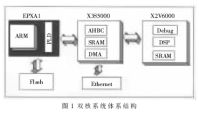

一種ARM+DSP協(xié)作架構的FPGA驗證實現(xiàn)

- 介紹了以ARM+DSP體系結構為基礎的FPGA實現(xiàn)。在其上驗證應用算法,實現(xiàn)了由ARM負責對整個程序的控制,由DSP負責對整個程序的計算,最大程度地同時發(fā)揮了ARM和DSP的各自優(yōu)勢。 ARM通用CPU及其開發(fā)平臺,是近年來較為流行的開發(fā)平臺之一,而由ARM+DSP的雙核體系結構,更有其獨特的功能特點:由ARM完成整個體系的控制和流程操作,由DSP完成具體的算法和計算處理。這樣,不但可以充分地發(fā)揮ARM方便的控制優(yōu)勢,同時又能最大限度地發(fā)揮DSP的計算功能。這在業(yè)界已逐漸成為一種趨勢。 本

- 關鍵字: ARM DSP FPGA 軟硬件協(xié)同驗證 SoC

fpga+dsp介紹

您好,目前還沒有人創(chuàng)建詞條fpga+dsp!

歡迎您創(chuàng)建該詞條,闡述對fpga+dsp的理解,并與今后在此搜索fpga+dsp的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對fpga+dsp的理解,并與今后在此搜索fpga+dsp的朋友們分享。 創(chuàng)建詞條

關于我們 -

廣告服務 -

企業(yè)會員服務 -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司