利用EP1C6Q240C8處理器的LCD滾屏設計

摘要:NIOSII嵌入式處理器以其設計靈活在嵌入式領域中得到廣泛應用。文章以T6963C控制的240×128 LCD液晶顯示屏模塊闡述了一種基于EP1C6Q240C8處理器的液晶顯示屏的滾屏顯示的軟硬件控制方法,并給出硬件原理圖與部分軟件代碼。本方案對于NIOSII系統其他模塊的開發具有借鑒意義。

關鍵詞:液晶顯示器;NiosII;可編程片上系統

0 引言

Nios II系列軟核處理器是Altera的第二代FPGA嵌入式處理器,其性能超過200DMIPS,Altera的Stratix、Stratix GX、Stratix II和Cyclone系列FPGA全面支持Nios II處理器。Nios II系列包括3種產品:Nios II/f(快速)——最高的系統性能,中等FPGA使用量;NiosII/s(標準)——高性能,低FPGA使用量;Nios II/e(經濟)——低性能,最低的FPGA使用量。這3種產品具有32位處理器的基本結構單元——32位指令大小,32位數據和地址路徑,32位通用寄存器和32個外部中斷源;使用同樣的指令集架構(ISA),100%二進制代碼兼容,設計者可以根據系統需求的變化更改CPU,選擇滿足性能和成本的最佳方案,而不會影響已有的軟件投入。另外,Nios II系列支持60多個外設選項,開發者能夠選擇合適的外設,獲得最合適的處理器、外設和接口組合,而不必支付根本不使用的硅片功能。本文采用CvcloneTM器件中的EP1C6Q24 0C8來實現雷達仿真電路顯示模塊的設計。

1 硬件設計

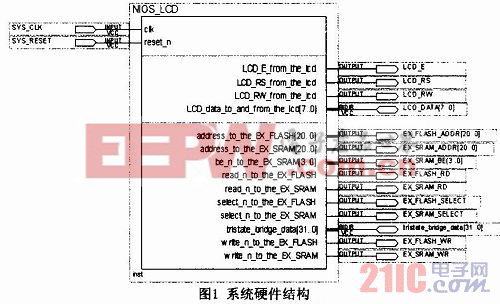

本系統的硬件設計結構如圖1所示,主要包括以下部分:

1.1 EP1C6Q240C8及其配置芯片

本文系統中的處理器選用的是采用AItera公司提供的Cyclone系列的EP1C6Q240C8,該芯片采用240腳的PQFP封裝,提供185個IO接口。

該芯片擁有5980個LEs;可提供92160bit的ram;芯片內部還自帶有2個鎖相環,可以在高速運行的時候保證系統時鐘信號的穩定性。

在Nios II的硬件電路,通常使用Altera串行配置器件來存儲FPGA配置文件*.Sof。

Altera串行配置器件可提供在系統編程(ISP)和多次編程能力,能夠使FPGA和配置器件能夠以最低的價格實現完整的可編程芯片系統(SO PC)解決方案。標準型配置器件,包括EPC2、EPC1、EPC1441、EPC1213、EPC1064和EPC1064V。本文使用EPC2配置器件。使用時,首先使用下載電纜將計算機生成的FPGA配置文件+.Sof使用programmer燒入EPC2配置器件中,然后由EPC2配置器件控制配置時序對FPGA進行配置,一次燒寫即可重復使用,編程完后可以脫離計算機工作。

LCD顯示屏相關文章:lcd顯示屏原理

lcd相關文章:lcd原理

評論