CPLD的DSP多SPI端口通信設計

本文介紹一種采用運動控制專用DSP芯片DSP56F801設計的超聲波電機運動控制裝置。由于該超聲波電機需要采用兩相四路對稱PWM信號來實現驅動控制,而DSP芯片無法直接產生所需PWM信號,采用軟件方法又會占用大量的DSP計算時間,于是設計了基于可編程邏輯器件(CPLD)的對稱PWM信號發生器。該信號發生器在DSP的控制下,可以實現輸出兩相PWM控制信號的占空比及相位差調節;同時采用具有SPI接口的可編程振蕩器LTC6903,實現在DSP控制下的PWM控制信號頻率調節。由此可見,為了實現DSP對PWM控制信號占空比、相位差及頻率的控制,需要采用適當的通信方式實現DSP與CPLD及LTC6903之間的控制信息傳遞。DSP56F801芯片具有一個SPI通信端口。本文在分析SPI數據傳輸時序關系的基礎上,設計并實現了基于CPLD的多SPI接口通信。

本文引用地址:http://cqxgywz.com/article/150661.htm1 工作原理

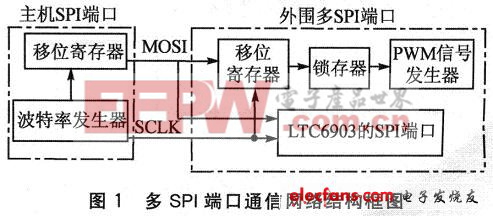

SPI是一個同步協議接口,所有的傳輸都參照一個共同的時鐘。在同一個SPI端口可以實現一個主機芯片與多個從機芯片的相連,這時主機通過觸發從設備的片選輸入引腳來選擇從設備,沒有被選中的從設備將不參與SPI傳輸。SPI主使用4個信號:主機輸出/從機輸入(MOSI)、主機輸入/從機輸出(MISO)、串行時鐘信號SCLK和外設芯片選擇信號(SS)。主機和外設都包含一個串行移位寄存器,主機通過向它的SPI串行移位寄存器寫入一個字節來發起一次傳輸。寄存器是通過MOSI引腳將字節傳送給從設備,從設備也將自己移位寄存器中的內容通過MISO信號線返回給主機。這樣,兩個移位寄存器中的內容就被交換了。外設的寫操作和讀操作是同步完成的,因此SPI成為一個很有效的串行通信協議。SPI端口的通信網絡結構框圖如圖1所示。為了使信號發生器輸出可調頻、調壓和調相輸出的兩相四路PWM波,需要DSP向CPLD電路輸出參數。這4個控制參數的傳遞是在小型的通信網絡中實現的。在該網絡中,DSP的SPI只是進行數據輸出端口的寫操作,即輸出電壓控制字、相位控制字和頻率控制字。數據流程:主機DSP向CPLD傳輸數據,在傳輸數據時,數據在MOSI引腳上輸出,同時數據在時鐘信號的作用下實現同步移位輸出。由于不需要從機向主機回送任何數據,主機在數據傳輸結束之后,結束這次傳送。由于SPI端口工作時沒有應答信號,并且數據在發送時無需校驗位,所以要求主、從器件的數據發送與接收必須完全符合設定的SPI時序要求,否則數據傳輸將出現錯誤。

2 基于CPLD的串口SPI設計

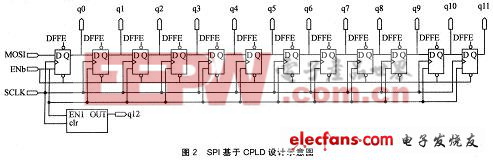

2.1 移位寄存器設計

本設計為一個12位的SPI串行接收端口。圖1中移位寄存器是由12個D觸發器和1個計數器組成的,實現移位接收和串并轉換。在傳輸過程中,先使能移位寄存器和計數器,啟動傳輸,同時計數器開始計數。當計數到16時,進位端輸出一個脈沖寬度的高電平脈沖,進行數據鎖存,其電路如圖2所示。

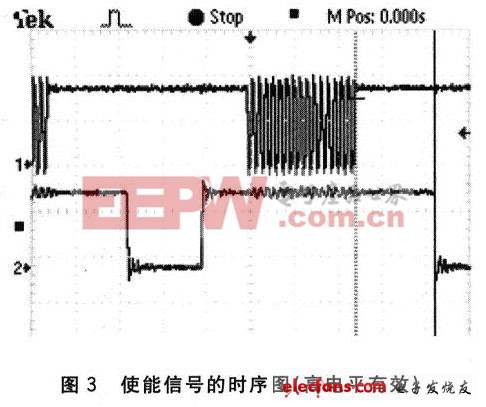

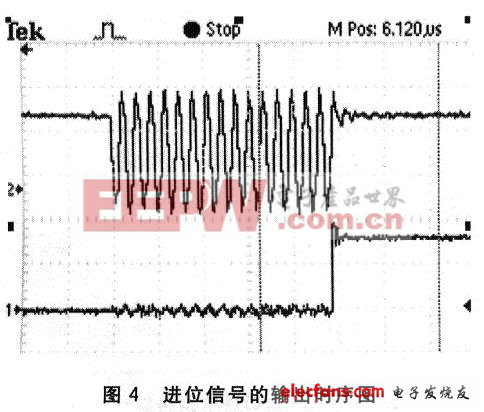

實驗中為保證時序正確,測出了使能信號和計數器進位脈沖的輸出時序,如圖3、圖4所示。其中十六進制計數器采用的是上升沿計數,在第16個上升沿到來時,跳變為高電平,保證數據的正確接收鎖存。

評論