基于SOPC技術的異步串行通信IP核的設計與實現

3 UART IP核設計

3.1 PLB Slave Single模塊介紹

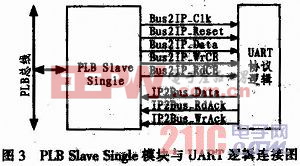

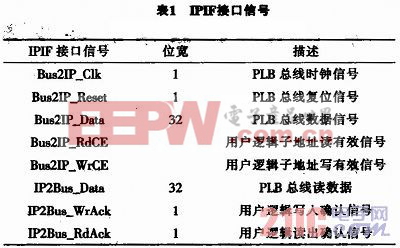

如上,UABT IP核作為PLB總線的從設備,必須提供PLB總線接口。但由于PLB總線協議復雜,實現其接口難度較大,Xilinx公司為了使用戶編寫的邏輯能夠方便的連結到PLB總線上,提供了一種PLB總線與用戶邏輯之間的接口模塊(IPIF,IP Interface),利用它簡化了PLB總線接口信號、總線協議和其他接口相關問題。IPIF接口邏輯中最簡單的模塊稱為PLB Slave Single模塊,它提供了一種輕量級的PLB總線接口,為PLB總線主設備提供了解析從設備地址空間,讀寫從設備寄存器/存儲空間等基本服務。本文設計的UARTIP核與MicroBlaze處理器之間僅通過寄存器的讀寫進行交互,PLB Slave Single模塊很好的滿足了該設計要求,因此采用PLB Slave Single模塊與UART邏輯共同構成了UART IP核。PLB Slave Single模塊與UART邏輯之間的連接關系如圖3所示,接口信號說明如表1所示。本文引用地址:http://cqxgywz.com/article/154802.htm

在系統中,UART IP核的內部寄存器組映射為處理器的某段地址空間,MicroBlaze處理器通過對該段地址的讀寫實現對UART IP核的訪問。當MicroBlaze處理器訪問UART IP核的某個寄存器時,PLB總線會產生相應的地址信號和讀寫信號,該信號被UART IP核中的PLB Slave Single模塊解析并生成相應的IPIF信號,UART IP核中的UABT邏輯響應該IPIF信號,完成寄存器的讀寫。

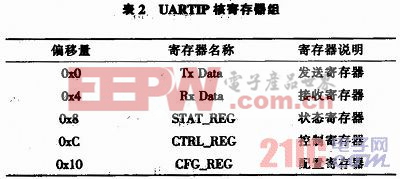

3.2 UART IP核寄存器組設計

文中設計的UART IP核提供了5個寄存器,如表2所示。其中發送寄存器和讀接收寄存器完成UART數據的發送和接收。狀態寄存器提供了UART IP核內部狀態,包括接收數據有效,發送FIFO滿,接收FIFO滿,奇偶校驗錯等狀態。控制寄存器提供了UART IP核復位功能。配置寄存器提供了波特率設置,奇偶校驗位設置等功能。

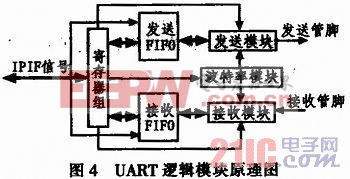

3. 3 UART協議邏輯模塊設計

本文設計的UART協議邏輯模塊主要包括波特率產生模塊,發送模塊,接收模塊,寄存器組等幾個部分,其結構如圖4所示。寄存器組說明如表2,其他幾個模塊的設計如圖4所示。

評論