應用于頻率合成器的寬分頻比CMOS可編程分頻器設計

1.3.1 傳統的檢測與置數邏輯設計

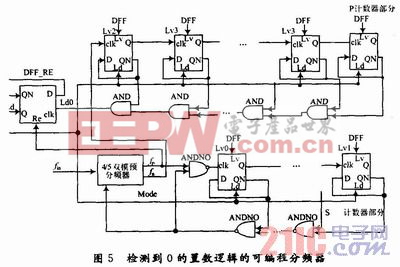

在傳統的基于雙模分頻器的可編程分頻器設計中,是對P計數器減計數到0時檢測,并通過一定的時序邏輯產生一個置數使能信號使得P計數器和S計數器進行置數。其檢測與置數邏輯電路如圖5所示,當P計數器減計數到0時,P計數器中每個D觸發器Qn端輸出都為1,這時級聯的與門邏輯輸出從0跳變到1,形成一個上升沿(為一個檢測信號)。這個上升沿作為帶有復位功能的D觸發器(DFF-RE)時鐘輸入,DFF-RE的復位端由4/5預分頻器輸出控制,即在嚴格的時序控制下,當檢測到P計數器減計數到0時產生一個上升沿信號,此時DFF-RE打開,這個上升沿信號使得DFF-RE輸出從0變為1,一段時間后DFF-RE關閉,故形成了一個置數脈沖,使得計數器重新置數。本文引用地址:http://cqxgywz.com/article/156400.htm

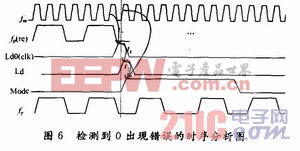

在這種結構中,檢測和置數的整個過程必須在輸入信號的一個周期內完成,從而限制了分頻器的工作頻率。下面通過對傳統檢測置數邏輯的時序分析來說明在輸入頻率較高時出現掉脈沖的現象,其時序圖如圖6所示,其中fin為分頻器的輸入信號,fp為4/5分頻器的輸出信號,同時作為DFF-RE的復位信號,Ld0為P計數器計數到0時的檢測組合邏輯電路輸出的信號,Ld為置數使能信號,即DFF-RE的輸出信號,Mode為控制4/5分頻器分頻數的信號。由圖中可知,在P計數器減計數到0時,檢測邏輯輸出一個脈沖(Ld0),從P計數到0到檢測脈沖信號產生有一個門延遲的t0,檢測脈沖到置數脈沖(Ld)的產生延遲時間為t1,Mode信號的產生延遲為t2。故從檢測到Mode信號上升沿的總延遲時間為t0+t1+t2,若這個總延遲時間大于了一個輸入信號的周期,如圖6所示,Mode信號控制的4/5預分頻器本該2次5分頻變為1次5分頻和1次4分

頻,從而出現了掉脈沖的現象,最終導致整個分頻比錯誤。

1.3.2 改進的檢測與置數邏輯設計

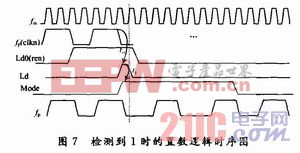

根據系統設計要求,分頻器工作的最高頻率需達到4.0 GHz,基于傳統的檢測置數邏輯的分頻器很難穩定的工作在此頻率下。因此,在該設計采用在P計數器減計數到1檢測,通過一定的時序控制下,當P計數器計數到0時置數,這樣檢測和置數的過程在2個輸入脈沖周期內完成,相對于計數到0檢測的分頻器,工作頻率可以提高2倍。以下具體分析改進后的檢測置數邏輯時序。在改進后的檢測置數邏輯中,如圖4所示,當P計數器減計數到0000001時,P計數器中DFF3~DFF7的QN端輸出都為1,因此AND0輸出由0變為1,AND0輸出反相信號作為DFF-RE復位端信號,而4/5分頻器輸出的反相信號作為DFF-RE的時鐘信號。其檢測和置數時序邏輯圖如圖7所示,當檢測到P計數到1后,DFF-RE便打開,置數脈沖的產生延遲為t0,Mode信號的產生延遲為t1,故由檢測到Mode上升沿信號的總延遲為t1+t2,相比圖6,少了一個門延遲,使得4/5預分頻器正確的進行了2次5分頻,避免了掉脈沖的現象。從對改進的檢測置數邏輯時序分析可知,改進后的設計使得可編程分頻器能夠工作在更高的頻率下。

評論