支持ONFI同步模式的NAND Flash控制器設計

3 同步模式設計

3.1 同步接口設計

支持ONFI2.0及以上的NAND Flash芯片既支持傳統的異步接口模式,也能通過配置工作在源同步的DDR接口模式下,從而達到速度的提高。如圖4所示,在同步工作模式下,增加了DQS信號,并將異步模式下的WE#信號變為CLK信號,RE#變為W/R信號。有很多文獻介紹了傳統異步接口模式下的NAND Flash控制器設計,本文不再贅述,以下開始介紹同步工作模式下的接口電路設計。本文引用地址:http://cqxgywz.com/article/162177.htm

當NAND Flash工作于同步接口模式時,接口I/O數據為DDR形式,讀寫操作時序見圖5,可以發現它非常類似于DDR SDRAM的時序,其中DQ[7:0]為數據,DQS為數據選通信號,其基本思想就是將兩組持續時間為一個時鐘周期的數據合并,使得在傳輸過程中一個時鐘周期的上升沿和下降沿都能傳輸數據,從而獲得傳輸速度的倍增。

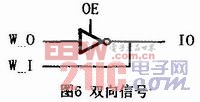

DQ和DQS均為雙向驅動信號,當進行寫操作時,由控制器進行驅動,當進行讀操作時,由Flash芯片內部進行驅動,本文雙向信號采用圖6方法實現,該結構需要置于整個設計的頂層,從而利于綜合的進行。

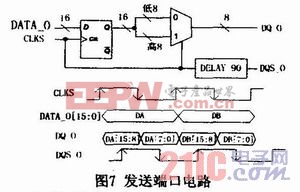

DQ與DQS信號間的相位關系對DDR接口非常重要。當對NAND Flash進行寫操作時,控制器必須產生一個與DQ數據信號中心對齊的DQS信號,所用發送端口電路如圖7所示,CLKS為同步接口模式下系統的整體時鐘。通過多路選擇器實現16bit數據DATA_O轉兩組8bit數據DQ_O輸出。CL-KS為高時對應DATA_O的高8bit數據,CLKS為低時對應DATA_O的低8bit數據,最后將CLKS進行移相作為DQS_O選通信號輸出。

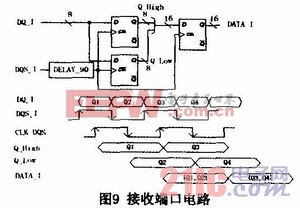

當從Flash存儲器件讀取的時候,Flash輸出的DOS信號是與DQ信號邊沿對齊的,需要對接收到的DQS信號進行相移使之與DQ信號中心對齊,以采到準確的數據。圖8是DQS移相后與DQ中心對齊的實際仿真波形圖。所用讀接口結構如圖9所示,首先將DQS_I選通信號進行移相,然后通過兩組分別為上升沿觸發和下降沿觸發的寄存器采樣與DQS_I上升沿和下降沿對齊的兩組8bit數據DQ_I,并通過一組同樣是上升沿觸發的寄存器將這兩組8bit數據合并成16bit數據。

實現讀寫操作的電路中都使用了DELAY單元,以達到移相的目的,DELAY單元可以由兩種方法實現:DLL和延遲線。將相移定為90°,是假設DQ和DQS是理想的源同步接口,并假定DQ和DQS經過芯片內部延時、PCB板上延時及pin腳延時是相同的,這樣能得到最理想的數據窗口。

評論