數字控制DC/DC變換器中ADC的設計

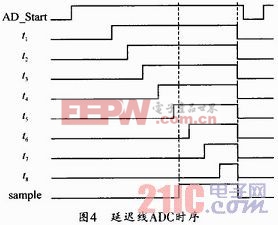

給定一個開始信號AD_Stan,經一定時間間隔后產生一個采樣脈沖信號sample,作為D觸發器的控制信號。在采樣信號有效時對D觸發器的輸入信號進行鎖存,將D觸發器的輸出信號送至譯碼電路得到最后的誤差信號。圖4是延遲線ADC的時序圖,假設圖2中n=8。在采樣信號有效時,AD_Start信號正好傳到第5個延遲單元,于是q1~q5輸出為1,q6~q8輸出為0。采樣電壓越大,延遲時間td越小,信號傳播得越快,輸出的溫度計碼中的1的個數越多。譯碼電路再將溫度計碼轉換為所需要的二進制碼。延遲線ADC即通過輸入電源對延遲鏈供電,根據延遲鏈延遲時間的大小來確定輸入的大小。

3 差分延遲線ADC

3.1 差分延遲線ADC結構分析

延遲線ADC結構簡單,功耗小,但易受工藝和溫度環境影響,且采樣信號需外部產生,增加了電路的復雜性,而且采樣信號的延遲大小會影響ADC量化電平的大小,使得系統輸出不易穩定。

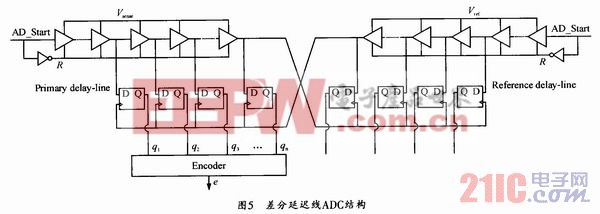

差分延遲線結構是對延遲線結構的一種改進,結構圖如圖5所示。差分延遲線ADC由兩條全同的延遲鏈組成,主延遲鏈(Primary delay-line)和參考延遲鏈(Reference delay-line)。參考延遲鏈可經主延遲鏈復制而來。兩條差分延遲鏈共用一個啟動信號AD_Start,使兩條延遲鏈的工作狀態完全相同。差分延遲鏈的兩個輸入分別是采樣電壓Vsense和基準。

電壓Vref,Vsense須小于Vref,根據電壓越大延遲越小的原理,參考延遲鏈先于主延遲鏈傳播完,將與主延遲鏈相連的D觸發器打開,對主延遲鏈上的Vsense進行采樣。這樣就實現了將采樣電壓與基準電壓作比較,再通過譯碼電路得到系統需要的數字誤差信號。

差分延遲線ADC的控制信號在內部產生,進一步簡化了電路結構。采用差分形式輸入,使得采樣電壓和基準電壓同時受到溫度和工藝偏差的影響,減少主延遲鏈的延時偏差。

p2p機相關文章:p2p原理

評論