數字控制DC/DC變換器中ADC的設計

3.2 差分延遲線ADC建模

設延遲鏈中的延遲單元個數為N,延遲時間td是VDD的函數:td=td(VDD),則有

即轉換時間Tc是分辨率Vq,延遲時間td以及延遲函數的斜率的函數。

圖6為0.13μm CMOS工藝下單個延遲單元與VDD的關系曲線。本文引用地址:http://cqxgywz.com/article/178716.htm

4 設計方法和仿真結果

延遲單元對精度要求較高,采用全定制設計,而譯碼電路對精度要求較低,采用基于標準庫單元設計,整體電路使用Hsim進行數模混合仿真。

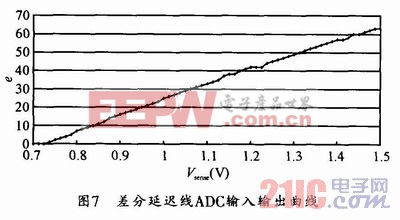

設計時,基準電壓為1.5V,工作頻率是1.5MHz,輸入電壓從0.7~1.5V線性上升,輸出為譯碼后的結果,即6位數字信號e。Vsense每增加或減少12.5mV,e增加或減少“1”,但e的最大值是63。圖7為0.13μm CMOS工藝下差分延遲線ADC的輸入輸出曲線,可以看出,差分延遲線ADC的輸出沒有明顯偏移,零輸入對應零輸出,線性度良好。

5 結束語

本文在分析了應用于數字控制DC/DC變換器中的ADC的特點的基礎上,研究了差分延遲線ADC的建模和實現。該差分延遲線ADC電路結構簡單,不需要外部電路產生控制信號,可抵消部分工藝偏差。該ADC轉換速率很快,功耗低,適合應用在高頻數字DC/DC變換器中。

p2p機相關文章:p2p原理

評論