SoC技術在FC芯片設計中的應用

FC收發通道模塊的設計

功能概述

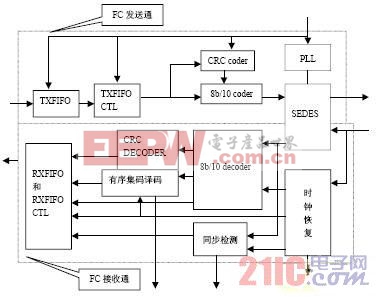

該模塊主要完成FC-2層幀的收發,包括:完成SERDES(串-并互相轉換模塊)與光電接口的連接、完成FC-1層的8b/10b編解碼、FC-2層幀級的CRC校驗和FC有序集碼的譯碼;同時利用內置存儲器構成FIFO與FC芯片后端模塊進行數據交換的緩沖區。

組成結構

該模塊分為“FC發送通道”和“FC接收通道”,如圖5所示。在收發通道之間提供多種自環測試的通路(未在圖中標出)。

“FC發送通道”主要由以下單元組成:

(1)并-串轉化單元;

(2)發送時鐘鎖相環;

(3)8b/10b編碼單元;

(4)CRC校驗生成單元;

(5)TX-FIFO發送控制單元;

(6)TX-FIFO數據輸入緩沖單元;

(7)自環控制單元。

“FC接收通道”主要由以下單元組成:

(1)串-并轉化單元;

(2)接收時鐘鎖相環;

(3)時鐘恢復單元;

(4)同步檢測單元;

(5)有序集譯碼單元;

(6)8b/10b解碼單元;

(7)CRC校驗單元;

(8)RX-FIFO發送控制單元;

(9)RX-FIFO數據輸出緩沖單元;

(10)自環控制單元。

圖5 FC通道結構框圖

評論