基于FPGA的數字選頻器設計

摘要:提出了一種基于FPGA的數字選頻器設計方案,該數字選頻器應用于八通道的GSM系統直放站,采用低成本的FPGA芯片Xilink Spartan-3A DSP XC3SD3400A進行數字信號處理。給出了較詳細的硬件設計方案,并通過Agilent Technologies N5230A網絡分析儀對數字選頻器進行了測量,被選出的有效相鄰信道之間的最小間隔能達到1MHz,能夠實現較好的選頻功能,可滿足實際應用的要求。

關鍵詞:FPGA;數字選頻器;GSM;直放站

0 引言

隨著移動通信的迅速發展,無論何種無線通信的覆蓋區域都將產生弱信號區和盲區,要架設模擬或數字基站成本太高,基礎設施也比較復雜,為此提供一種成本低、架設簡單,卻具有小型基站功能的直放站是很有必要的。GSM移動通信系統在我國經過多年的發展,目前已經擁有最大的網絡覆蓋規模、最多的用戶數、種類多樣的業務,在我國移動通信市場中占有重要的地位。本文對GSM直放站的數字無線選頻器進行設計,以達到低成本擴大無線網絡覆蓋范圍和優化網絡的目的。

1 系統總體結構

GSM900中上下行信道各120個,帶寬為24 MHz,其中上行頻段為885~909 MHz,下行頻段為930~954 MHz,數字選頻器工作效果示意圖如圖1所示。

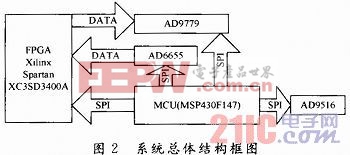

如圖1所示,數字選頻器就是僅放大選中的頻段,抑制未選中的頻段,實現降低信道間干擾的目的。系統總體結構框圖如圖2所示。數字選頻系統主要由A/D模塊、FPGA可編程邏輯器件模塊、D/A模塊以及MCU管理模塊四部分組成。

軟件無線電的思想是將無線電收發信機的數字化點(A/D/A)盡可能靠近天線,理想的情況是在天線的后端進行射頻采樣,數字化之后,所有的處理都可以用很靈活的方法實現。但是由于目前ADC器件性能的限制,還無法達到在射頻端進行數字化,在中頻實現數字化是一個較妥的方案。

GSM直放站數字選頻系統就是利用數字處理的手段實現濾波器功能,以替代現有直放站中的模擬選頻模塊。本系統通過AD6655接收下變頻后的模擬中頻信號,通過A/D采樣將模擬信號轉換為數字信號,采樣頻率為122.88 MHz。然后由FPGA按預定算法對來自AD6655的數字信號進行數字處理,處理后的結果再由AD9779轉換成模擬信號。MCU通過SPI接口對AD6655,AD9779和AD9516的寄存器進行配置,并與FPGA之間進行通信。

評論