基于FPGA的交通燈系統控制設計

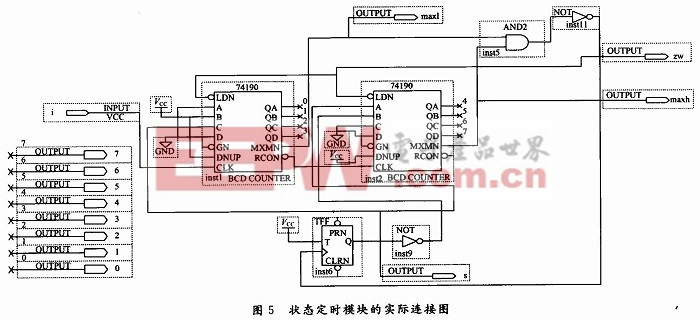

狀態計時電路由兩片74190級聯而成,構成22和16自翻轉的電路。其要解決的核心問題包括置數,翻轉和借位。根據74190芯片的特點,可分析其實現原理如圖4所示,通過溢出信號RCON的上升沿實現借位,使得數字能夠從20到19,個位向十位借位,順利過渡。

置數和翻轉之間有先后關系,即須先置數后翻轉。如表3所示,分析兩個BCD碼各位特點,可知兩者D7D6D3D0位均為1,D1位均為0,而D5D4D2位不同,如圖5,D5D4D2位由狀態電平S來控制,當為I狀態時,計數器的預置的數為D5=0,D4=D2=1,而為J狀態時,計數器的預置的數為D5=1,D4=D2=0,根據74190的功能,將2片74190的MAX/MIN引出,通過與非門,分別連在高位和低位的LDN置數端,通過分析可知,當計數器從01減到00時候,高低位的MAX/MIN均為高電平,經過與非門以后為低電平,74190被置數,其置數值由狀態S來決定,S是由LDN端信號經

過一個T’觸發器決定的,即LDN信號每置數一次,S翻轉1次,從而區分16和22狀態。按這個結構,可分別置數16和22,使其實現自翻轉。

圖5為狀態定時模塊的實際連接圖。

1.3.3 時間顯示

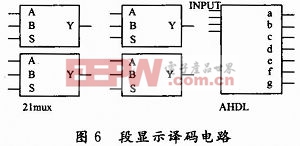

時間顯示要用到7段顯示譯碼電路,由于是兩位BCD碼,故用二選一數據選擇器。選擇端S接一個頻率很高的方波(如1 kHz);數據比較器的輸出和1 Hz脈沖作為AHDL模塊的輸入,即可正確顯示時間。

![]()

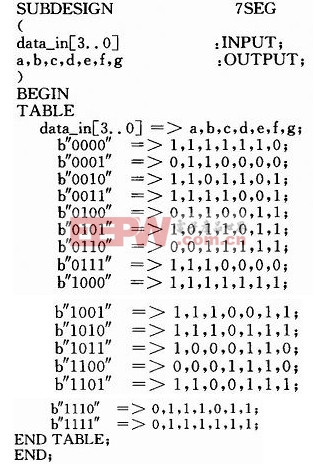

為正確顯示時間,用AHDL文件自編譯碼真值表如下:

評論