基于FPGA的交通燈系統控制設計

摘要:為了對交通燈系統進行精確控制,采用FPGA實驗板,在QuartusⅡ軟件環境下,分別實現脈沖發生模塊、狀態定時模塊、交通燈顯示模塊、時間顯示模塊,進行仿真實驗和硬件下載,獲得的測試結果滿足設計要求。由于采用了EDA技術,使數字系統設計的效率顯著提高。

關鍵詞:FPGA;QuartusⅡ;交通燈;數字系統設計

目前交通燈廣泛應用于道路交通建設中。本文設計一個十字路口交通燈控制電路,要求東西、南北兩條干道的紅、綠、黃交通燈按要求循環變化,并以倒計時方式指示干道通行或禁止的維持時間。在QuartusⅡ軟件環境中設計、仿真,并在FPGA實驗板上實現所設計電路的功能。

1 系統概述

1.1 設計思想

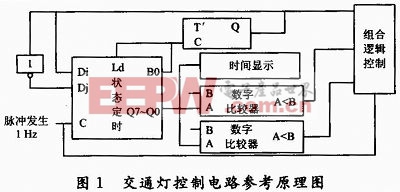

基于FPGA的交通燈系統控制設計包括4大模塊,分別為脈沖發生、狀態定時、交通燈閃爍的控制、閃爍時間的控制,基本原理如圖1所示。

1.2 總體工作情況

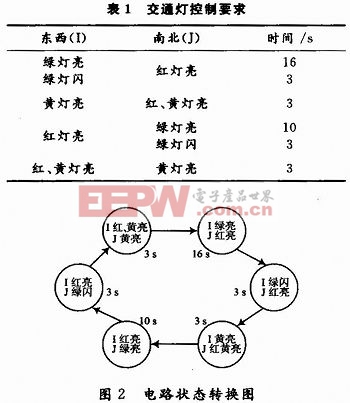

交通燈控制要求如表1所示。

該設計的交通燈控制分為6個狀態。由于各狀態持續時間不同,所以電路的核心控制部分是狀態機和定時器,狀態機在定時器觸發下周期性循環,狀態碼控制6個燈以一定的規律變化。變化情況如圖2所示。

系統脈沖由FPGA開發板晶振經過分頻電路實現。狀態定時由74190可逆十進制計數器和T’觸發器實現,只要置數合理,翻轉信號到位,就可以使電路在東西(I)、南北(J)兩個控制狀態間翻轉。紅、黃、綠燈的閃爍由7485數字比較器和組合邏輯控制,其中7485數字比較器用于比較計數器當前持續狀態和所需要的狀態全部時間,并做出相應的變化。組合邏輯控制由AHDL文件編寫真值表實現。時間顯示由AHDL文件編寫真值表實現,輸入正確的邏輯,七段譯碼電路即能得到正確的時間顯示。

1.3 各功能的組成

整個電路可以分為4大部分,包括脈沖發生、狀態定時、時間顯示和數字比較一組合邏輯控制。

1.3.1 脈沖發生

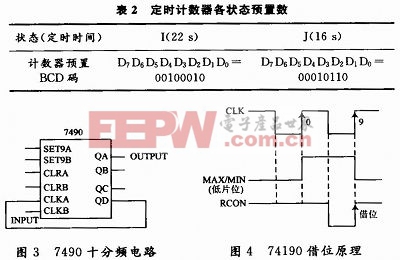

脈沖發生器為整個系統提供驅動,將輸入端分配給FPGA實驗板的PIN55引腳,則會由實驗板上產生頻率為10 MHz的輸入脈沖,用7片7490,每一級都構成10分頻電路,使頻率從10 MHz降低為1Hz。

1.3.2 狀態定時

狀態定時可由預置BCD碼初值的74190級聯實現,構成減計數器。級聯原則是:低位計數器從全0狀態變為最大碼值狀態時可使高位計數器減1。級聯方式分為異步和同步兩種,本文采取的是異步級聯方式,即低位計數器溢出信號控制高位計數器的記數脈沖輸入端。可根據計數器的時鐘觸發方式,在低位計數器狀態碼從全“0”變為最大碼值的瞬間,為高位計數器提供有效的計數脈沖邊沿。具體做法是將低片位的溢出信號RCON端口接到高片位的計數脈沖CLK,實現兩位BCD碼的置數、翻轉和借位,使系統表示的數字能在22~16之間循環。

74190功能說明:

(1)GN為計數器使能控制端,低電平有效。當GN為高電平時,禁止計數。

(2)DNUP為計數方式控制,接高電平為減計數,接低電平為加計數。

(3)LDN為異步預置數控制。當LDN為低電平時,計數器狀態QD,QC,QB,QA分別等于D,C,B,A。

(4)計數器位序由高至低順序為QD,QC,QB,QA。QD為最高位MSB,QA為最低位LSB。

(5)計數脈沖CLK上升沿有效。

(6)當計數器輸出QDQCQBQA為十進制加計數的最大狀態碼“1001”或為減計數的最小狀態碼全“0”時,極值狀態碼指示MAX/MIN輸出為高電平。

(7)當極值狀態碼指示MAX/MIN為高電平且CLK為低電平時,溢出信號RCON為低電平,即RCON與計數脈沖同步。

系統記數脈沖為1 Hz時,如表2所示,當I狀態(東西控制狀態)的定時時間為22 s,計數器應該先預置22的BCD碼;同理,J狀態(南北控制狀態)之前應該預置16的BCD碼。

評論