基于FPGA的交通燈系統控制設計

1.3.4 數字比較一組合邏輯控制

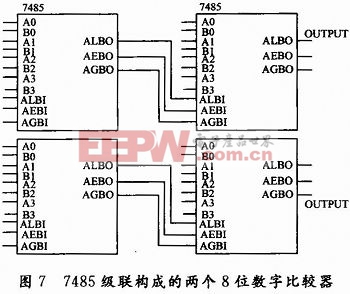

該模塊將狀態定時模塊輸出的時間與時間節點進行比較,從而確定電路處于22 s或者16 s的具體的某個狀態。由表1可知,東西(I)或南北(J)的控制狀態都有3個階段的控制邏輯,分別對應3個時間段:1~3 s,4~6 s和大于6 s,因此,采用數字比較器進行比較,確定定時值小于4 s或大于6 s,方法如圖7所示,采用4片7485數字比較器,兩兩級聯,其中一個由狀態定時模塊的輸出與4即二進制0100比較;另一個由狀態定時模塊的輸出與6即二進制0110比較。本文引用地址:http://cqxgywz.com/article/191050.htm

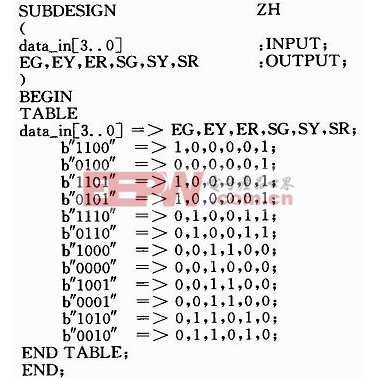

編寫組合邏輯真值表,將狀態信號S,兩個數字比較器的輸出Y1,Y2和1 Hz脈沖作為輸入,各個燈的狀態作為輸出。從而根據邏輯關系得出對應時間電路的狀態,控制紅、黃、綠燈處于不同的狀態。S判斷電路處于22 s狀態還是16 s狀態,Y1,Y2區分東西、南北六個階段狀態,1 Hz脈沖實現綠燈閃爍。

2 電路的組構與調試

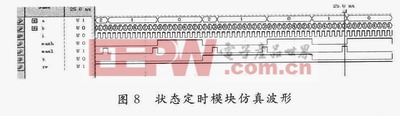

來用QuartusⅡ軟件設計各個模塊,并進行仿真。確認結果后,下載至FPGA實驗板中,進行相應的硬件調試,調試結果與仿真結果相一致。圖8為仿真波形,系統上電需要調整的過程,因此電路正常工作前重復了22s的狀態。

評論