利用FPGA協(xié)處理提升無線子系統(tǒng)性能

您可以顯著提高無線系統(tǒng)中信號處理功能的性能。怎樣提高呢?有效方法是利用FPGA結(jié)構(gòu)的靈活性和目前受益于并行處理的FPGA架構(gòu)中的嵌入式DSP模塊。

本文引用地址:http://cqxgywz.com/article/191593.htm常見于無線應用中這類處理包括有限沖激響應(FIR)濾波、快速傅里葉變換(FFT)、數(shù)字上下變頻和前向誤差校正(FEC)。Xilinx Virtex-4和Virtex-5架構(gòu)提供多達512個并行嵌入式DSP乘法器,這些乘法器的工作頻率高于500MHz,最高可提供256 GMAC的DSP性能。

將需要高速并行處理的工作卸載給FPGA,而將需要高速串行處理的工作留給處理器,這樣即可在降低系統(tǒng)要求的同時優(yōu)化整體系統(tǒng)的性價比。

子系統(tǒng)劃分選擇方案

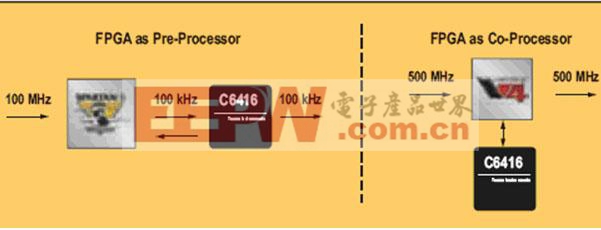

FPGA可與DSP處理器一起使用,作為獨立的預處理器(有時是后處理器)器件,或者作為協(xié)處理器。在預處理架構(gòu)中,F(xiàn)PGA直接位于數(shù)據(jù)通路中負責信號預處理,預處理后的信號可以高效又經(jīng)濟地移交給DSP處理器進行速率較低的后續(xù)處理。

在協(xié)處理架構(gòu)中,F(xiàn)PGA與DSP并列而置,后者將特定算法函數(shù)卸載給FPGA,以便實現(xiàn)比單獨采用DSP處理器能達到的速度更高的處理速度。FPGA的處理結(jié)果傳回DSP,或者送至其他器件進一步進行處理、傳輸或存儲(圖1)。

選擇預處理、后處理還是協(xié)處理,常常取決于在處理器和FPGA之間移動數(shù)據(jù)所需的時序余量及其對整體延遲的影響。雖然協(xié)處理解決方案是設計人員最常考慮的拓撲結(jié)構(gòu)(主要是因為DSP可以更直接地控制數(shù)據(jù)移交過程),但這并不一定總是最佳的總體策略。

例如,最新的3G LTE規(guī)范將傳輸時間間隔(TTI)從HSDPA的2ms和WCDMA的10ms縮短到了1ms。這實質(zhì)上是要求從接收器一直到MAC層輸出之間的數(shù)據(jù)處理時間短于1,000?sec。

圖1:FPGA 用作預處理器和協(xié)處理器的解決方案。

評論