構建節能AI加速器的硬件策略有哪些?

人工智能 (AI) 應用每天都在擴展到更多行業。然而,這些人工智能系統使用的能源量已成為一個重大問題。現代深度神經網絡需要大量的計算能力。

本文研究了構建節能 AI 加速的五種關鍵硬件策略:專用加速器架構、模擬內存計算、異構計算系統、神經形態計算和 3D 芯片堆疊技術。

專用加速器、硬件架構

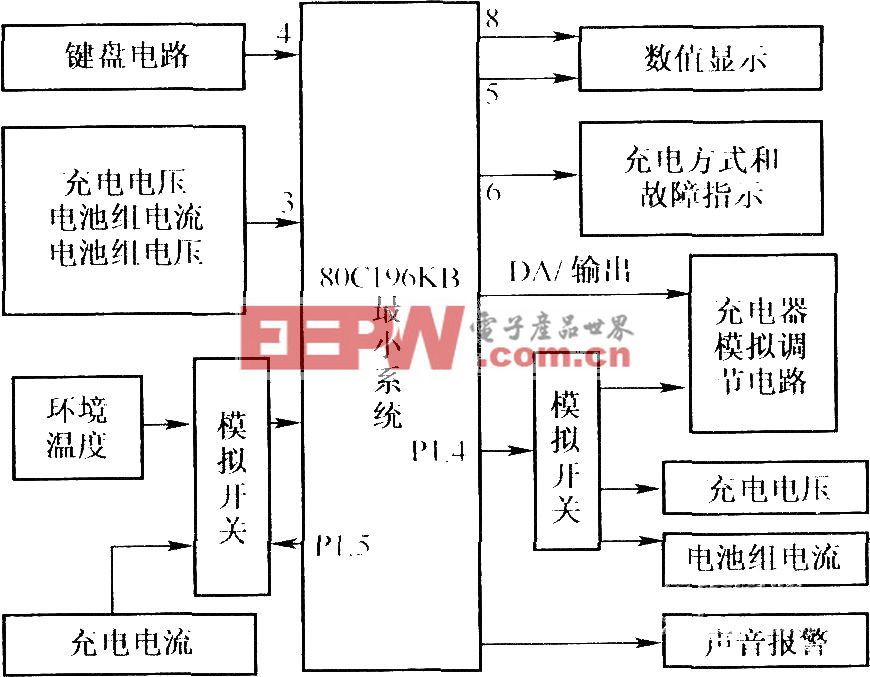

人工智能系統需要特殊的計算機芯片,在運行人工智能模型時,這些芯片比普通 CPU 工作得更好。普通 CPU 無法足夠有效地處理 AI 任務并消耗過多的功率。為了解決這個問題,工程師們創建了四種主要類型的專用加速器架構,如圖 1 所示。每種類型的硬件加速器都有其優勢,最適合不同類型的 AI 工作負載:

圖 1.不同的專用 AI 加速器硬件架構。(圖片來源:AI加速器研究院)

圖 1.不同的專用 AI 加速器硬件架構。(圖片來源:AI加速器研究院)

圖形處理單元 (GPU) 具有數千個具有高內存帶寬的并行計算核心,使其成為深度學習中常見的矩陣運算的理想選擇。他們的架構包括專門的張量核心,可以加速人工智能作,同時保持跨各種框架的靈活性。

神經處理單元 (NPU) 專為 AI 推理而設計,具有針對矩陣乘法和卷積運算優化的多個計算單元。它們的架構包括片上存儲器,以減少數據傳輸開銷并提高吞吐量,尤其是在卷積神經網絡方面表現出色。

現場可編程門陣列 (FPGA) 提供數百萬個可編程門,可針對特定 AI 任務進行重新配置。這種靈活性允許優化特定的神經網絡架構,同時實現低延遲,使其對實時應用程序很有價值。

專用集成電路 (ASIC) 通過專門為特定人工智能模型量身定制的定制設計架構提供最高的能源效率。雖然缺乏靈活性,但它們為專用應用提供了卓越的每瓦性能。

每種架構都代表了靈活性、性能和能源效率之間的不同權衡,允許開發人員根據其特定的 AI 推理要求和部署限制選擇最佳硬件策略。

模擬內存計算架構

模擬內存計算 (AIMC) 通過在存儲數據的地方執行計算來解決馮·諾依曼瓶頸,而不是在單獨的處理單元和內存單元之間移動信息。圖 2 說明了相變存儲器 (PCM) 器件如何通過利用基本物理原理的交叉陣列實現這種方法。

圖 2.模擬內存計算的工作原理。顯示了從基本存儲設備到可以直接在內存中運行不同類型神經網絡的完整系統的進展。(圖片來源:ResearchGate)

矩陣向量乘法是神經網絡中的主要運算。這些作使用歐姆定律和基爾霍夫定律執行。施加到字線的輸入電壓與存儲的電導值相互作用,產生與所需計算結果成正比的電流。

AIMC tile 架構集成了數模轉換器和模數轉換器。這些組件與數字系統接口,同時保持模擬計算效率。這種方法通過消除數據移動開銷并實現顯著的并行性(同時執行數百萬個作)來提供能源優勢。

非易失性存儲器特性進一步降低了靜態功耗。ALPINE 框架在多種神經網絡類型(例如 MLP、CNN、RNN 和 LSTM)中展示了這些優勢。與傳統實施相比,它可以實現高達 20.5 倍的性能加速和 20.8 倍的能源改進。然而,在管理精度限制和設備可變性方面仍然存在挑戰。

異構計算架構

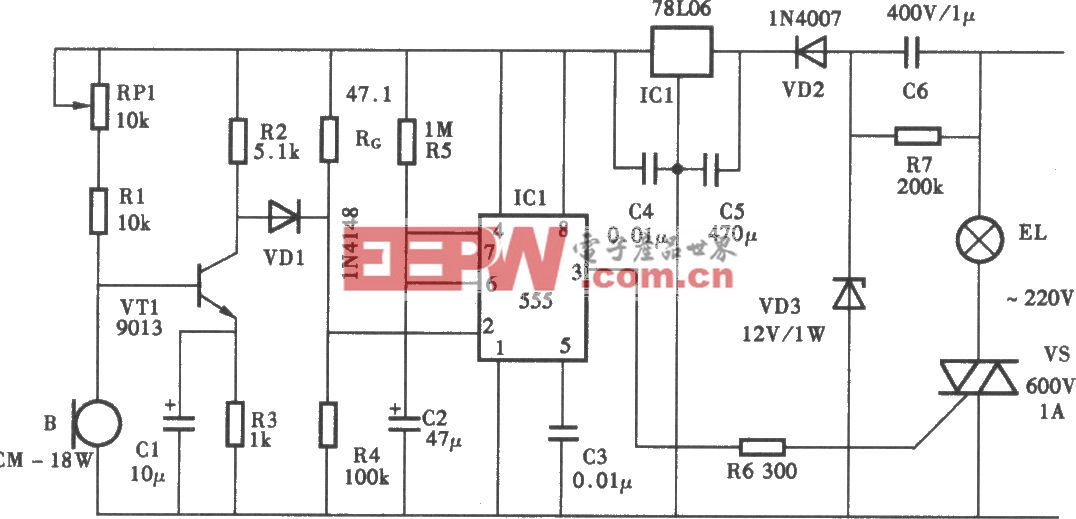

異構計算架構通過部署多個專用處理單元來協同處理人工智能工作負載的不同方面,從而提高能源效率。圖 3 說明了瑞薩電子的 DRP-AI3 實現,其中 AI 加速器與動態可重構處理器 (DRP) 和傳統 CPU 內核一起工作。這種方法認識到人工智能應用程序需要不同的計算模式。這些范圍從神經網絡推理到基于算法的處理和系統控制。每種模式都針對不同的硬件類型進行了優化。

圖 3.用于異構架構中 AI 任務的專用硬件,用于其他算法的可配置硬件,以及用于系統控制的常規處理器。(圖片來源:瑞薩電子)

圖 3.用于異構架構中 AI 任務的專用硬件,用于其他算法的可配置硬件,以及用于系統控制的常規處理器。(圖片來源:瑞薩電子)

AI 加速器組件使用專用 MAC 單元和優化的數據流處理計算密集型神經網絡作,而可重新配置的 DRP 處理器動態調整其電路配置以進行流數據處理、圖像預處理和池化作。CPU 管理系統級任務并提供編程靈活性。

這種分工使每個處理單元能夠在其專業領域內高效運行,從而避免了與強制通用硬件處理專門任務相關的能源損失。合作設計取得了顯著的成果,硬件與軟件的協調提供了高達 10 倍的性能提升,同時保持了對不同 AI 模型類型的靈活性。

跨異構組件的多線程流水線進一步優化了資源利用率,展示了戰略任務分區如何提高整體系統能效。

神經形態計算

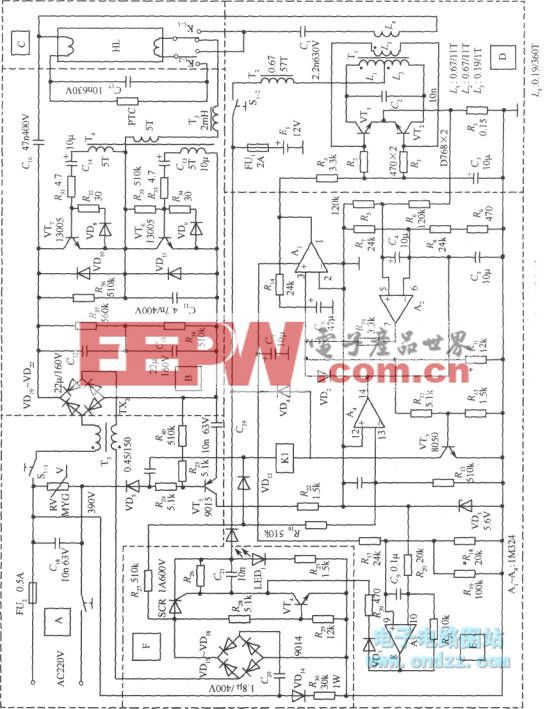

神經形態計算復制了人腦使用能量的方式。這種受大腦啟發的方法通過使用憶阻器作為電子突觸來改變我們構建計算機的方式。這些憶阻器結合了處理和存儲器通常單獨執行的工作。圖 4 顯示了三維神經形態架構如何構建分布式計算網絡。在這些系統中,憶阻器件同時用作存儲和計算元件。這種方法創建了非馮諾依曼系統,其工作方式與普通計算機非常不同。

圖 4.顯示 (a) 2D 神經網絡,(b) 3D 實現,(c) 神經元-突觸連接的 3D 神經形態系統。(圖片:IntechOpen)

與傳統的 2D 方法相比,3D 實現具有優勢,因為它在神經元層之間提供高連接性,同時解決影響傳統設計的路由擁塞問題。憶阻突觸能夠通過自適應學習能力實現并行數據處理,以類似于生物神經網絡的事件驅動方式處理信息。

該架構支持各種神經形態計算方法,包括分布式、集中式和自適應神經形態計算架構。

調查數據表明,尖峰神經網絡加速器表現出更高的能效,平均消耗 0.9 瓦,而非尖峰實現的平均功耗為 1.7 瓦。它使神經形態計算非常適合需要智能、自適應行為的低功耗邊緣應用。

3D芯片堆疊

三維芯片堆疊解決了平面半導體縮放的物理限制,同時通過縮短互連距離來提高能效。圖 5 說明了兩種主要的 3D RRAM 集成策略:水平 3D RRAM (H-RRAM) 和垂直 3D RRAM (V-RRAM) 結構,它們將傳統的 2D 橫桿陣列擴展到三維空間。這種垂直縮放通過面積縮放實現了器件密度的顯著提高。

圖 5.3D 芯片堆疊架構可提高器件密度和能效。(圖片來源:ResearchGate)

能效提升源于縮短的信號路徑和減少的互連電容,直接降低了功耗,同時實現了高連接性系統。硅通孔促進層間通信,創建適合密集神經網絡實現的并行數據處理能力。

隨著層數的增加,V-RRAM架構被證明特別具有成本效益。臨界光刻掩模的數量仍然相對獨立于堆疊層。這與 H-RRAM 不同,H-RRAM 的模板要求是線性擴展的。這種 3D 方法允許將內存和處理元素組合到一個塊中。這使得神經網絡加速器具有更高的密度和更高的能效,適用于需要緊湊性和速度的下一代人工智能應用。

總結

構建節能的 AI 加速器包括許多硬件策略。這些范圍從專用架構和模擬內存計算到異構系統、神經形態設計和 3D 集成技術。人工智能加速的未來在于巧妙地結合各種技術。成功將取決于硬件-軟件協同設計。這意味著算法優化和硬件能力必須同步發展,以提高人工智能系統的能源效率。

評論