什么是JESD209-6,為什么它對邊緣AI很重要?

JESD209-6 是 JEDEC 最近發布的 LPDDR6(低功耗雙倍數據速率 6)標準,代表了存儲技術的重大飛躍,特別是對于功率預算有限的設備而言。它對于下一代移動設備、人工智能應用和邊緣計算至關重要,在這些領域,高性能和能效至關重要。它還有望幫助限制數據中心應用的功耗。

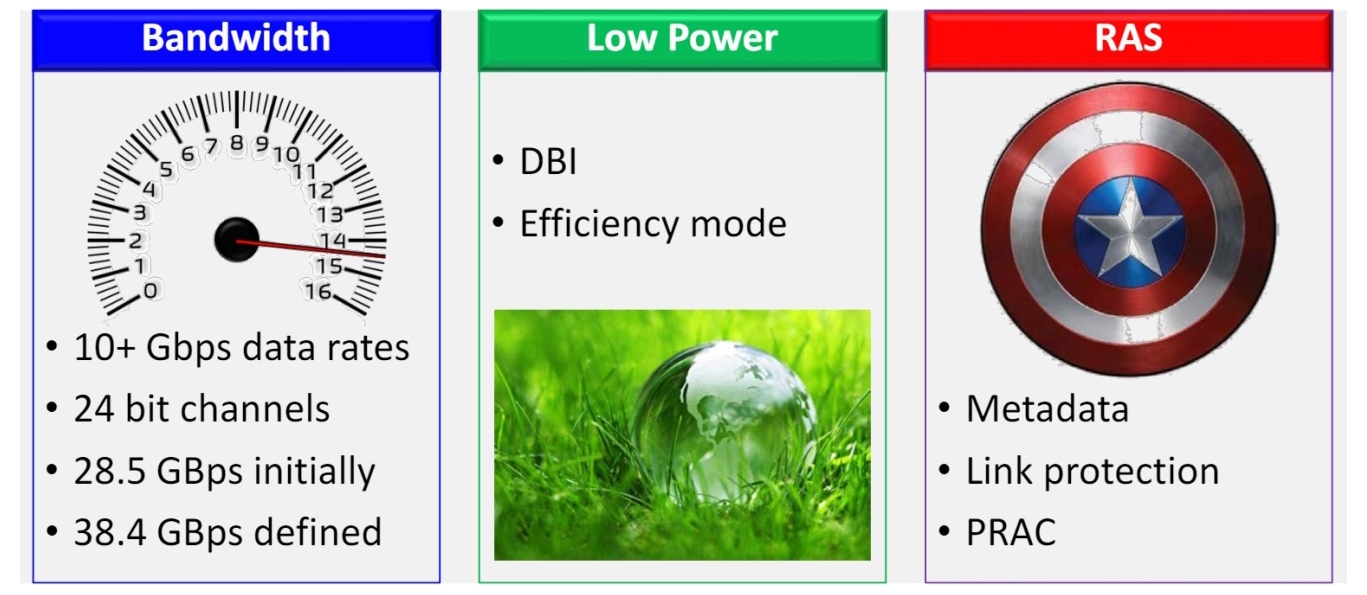

一些關鍵功能和改進包括增加帶寬(路徑高達 38.4 Gbps)、更低的能耗以及增強的可靠性、可用性和可維護性 (RAS)。

例如,數據總線反轉 (DBI) 旨在提高內存作的性能和能效。每行激活計數 (PRAC) 通過監控和管理行激活來幫助維護 DRAM 數據完整性,防止潛在的數據損壞。(圖 1)。

圖 1.LPDDR6支持更高的帶寬、更低的功耗和更高的可靠性。(圖片來源:Tweak Town)

圖 1.LPDDR6支持更高的帶寬、更低的功耗和更高的可靠性。(圖片來源:Tweak Town)

深入研究細節

架構和設計改進的結合使 LPDDR6 能夠在 64 位總線上提供高達 38.4 GB/s 的最大帶寬,是 LPDDR5 初始能力的兩倍。LPDDR6 還提供了更大的靈活性,可實現更微調和性能優化。

雙子通道架構支持每個子通道 12 條數據信號線 (DQ) 和 4 個專用命令/地址 (CA) 信號,從而實現更快的數據訪問,并能夠根據需求變化優化通道性能。

LPDDR6 中的信道寬度已從 LPDDR5 中的 16 位增加到 24 位。結合雙子通道,更寬的通道進一步增強了整體內存帶寬。這可能導致智能手機的帶寬從 64 位增加到 96 位,筆記本電腦的帶寬從 128 位增加到 192 位。

最后,LPDDR6 支持 32 字節和 64 字節突發之間的實時突發長度控制,有助于優化帶寬和功耗。這對于處理可變 AI 工作負載的邊緣設備尤為重要。

有幾種降低功耗的新工具,包括 DBI 和添加第二個電源域。DBI支持功耗和降噪。

如果達到“0”位的預定閾值,則整個字節將反轉,所有位從 0 翻轉到 1,反之亦然。專用的 DBI 位用于指示數據已反轉。反相旨在減少高到低轉換的次數,從而降低開關噪聲和功耗。

LPDDR6 還支持更復雜的電源管理,具有兩種效率模式。靜態效率模式專為持續的高吞吐量 AI 工作負載而設計。動態效率模式有助于優化低帶寬場景(如處理傳感器數據)的性能。

在動態效率模式下運行時,使用單個子通道。此外,LPDDR6 還增加了第二個電壓域 VDD2,支持低活動期間的低功耗動態電壓和頻率縮放 (DVFSL)。

可靠性

當然,如果數據不可靠,高帶寬和低功耗就沒有用。LPDDR6 具有多項專門用于確保 RAS 的功能。PRAC 監控和管理行激活,幫助確保數據完整性。內存內置自檢 (MBIST) 支持原位測試,有助于診斷和排除潛在問題。

LPDDR6 支持片上糾錯碼 (ECC),用于檢測和糾正硬件級別的內存錯誤,支持命令/地址 (CA) 奇偶校驗,用于檢測命令和地址傳輸期間的錯誤。

如果檢測到錯誤,錯誤清理功能有助于在存儲單元中發生錯誤時糾正錯誤,以免它們累積并影響系統可靠性。分拆元模式支持為關鍵任務分配特定內存區域,隔離和保護重要數據和作。

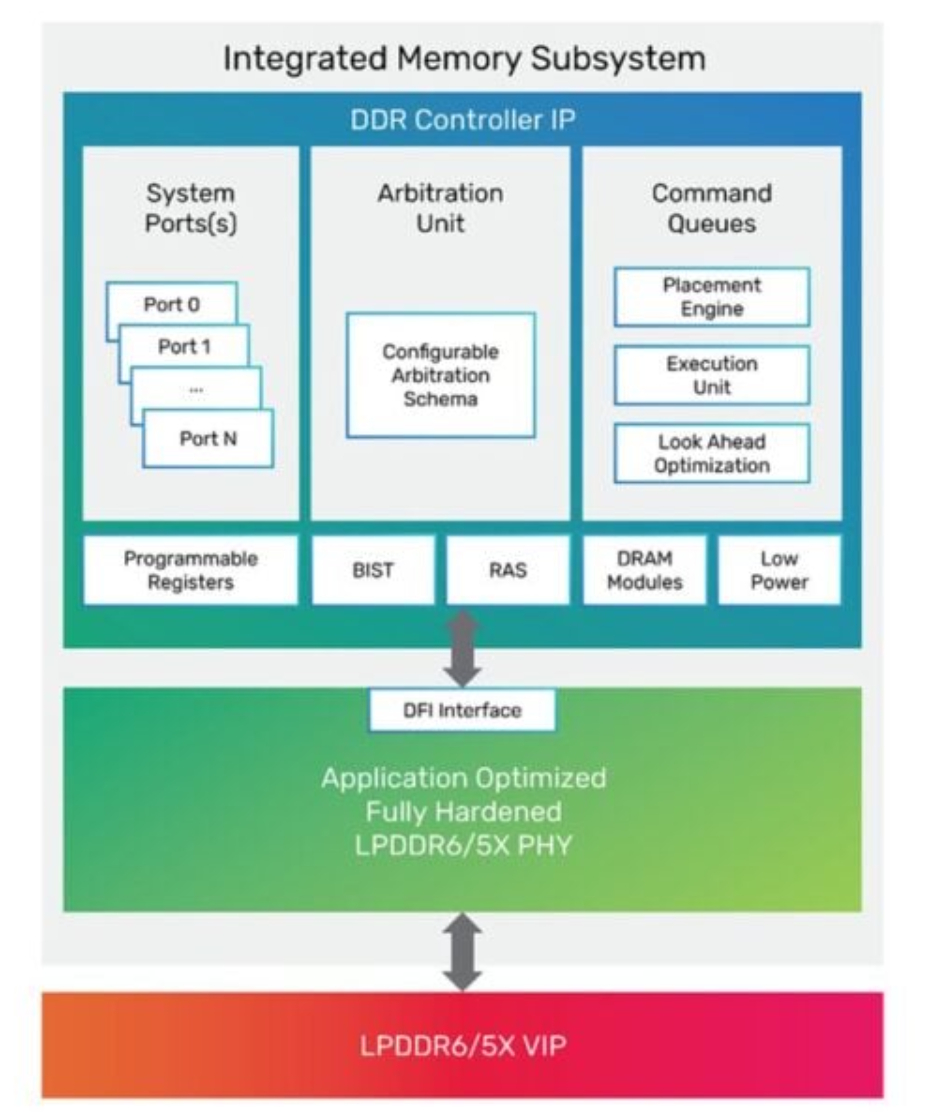

圖 2.同時支持 LPDDR6 和 LPDDR5 的內存控制器 IP 框圖,旨在最大限度地提高功耗、性能和面積 (PPA)。(圖片來源:Cadence)

LPDDR6 內存控制器

LPDDR6 內存控制器已經上市。有些同時支持 LPDDR6 和 LPDDR5,以實現兩代技術之間的平滑過渡。控制器支持原生集成到單片系統 (SoC) 和多芯片解決方案中。

支持高級內存接口,如 Arm AMBA AXI 總線。內存控制器以軟寄存器傳輸電平 (RTL) 宏的形式作為可重用塊提供(圖 2)。

總結

JESD209-6,通常稱為 LPDDR6,已針對在智能手機和筆記本電腦等功率有限的平臺上運行 AI 應用程序進行了優化。與 LPDDR5 相比,它提供了更高的帶寬、更低的能耗以及增強的可靠性、可用性和可維護性。最初的 LPDDR6 控制器 IP 也支持 LPDDR5,以簡化向新技術的遷移。

評論