Palladium模擬器和用于PCIe調試的FPGA有什么區別?

PCI-SIG外圍組件互連 Express Gen5(PCIe Gen5)是一種系統協議,主要用于系統中高速的數據傳輸。PCIe Gen5可實現32 Gb/s的傳輸速率。PCIe 幾乎集成在所有計算機系統中,包括服務器。

PCIe是一種復雜的協議,包括鏈路訓練、TLP生成和事務、不同的有效載荷傳輸、錯誤TLP、流量控制以及RC和EP模式下的恢復狀態驗證。在對整個系統進行驗證之前,驗證協議至關重要。

驗證工程師通過通用驗證方法(UVM)測試平臺參與驗證PCIe協議。除了驗證設置外,仿真工程師還提供驗證PCIe協議及軟件開發的平臺。本文介紹了驗證 PCIe Gen5 協議及 Palladium 模擬器軟件所需的步驟。

模擬器用于PCIe驗證的硬件需求

要在模擬器上驗證PCIe Gen5協議,需要滿足以下條件:

PCIe Gen5 RTL/IP

軟件或作系統——都可以加載到模擬器中

PCIe Gen5 虛擬 SpeedBridge

這種硬件配置是驗證PCIe Gen5協議所必需的:

鈀金模擬器

一個Linux InfiniBand(IB)主機

PCIe Gen5 SpeedBridge 或 PCIe Gen5 高密度速度橋(HDSB)

支持Gen3、Gen4或Gen5的SSD版本

底座連接PCIe、SpeedBridge和SSD。

環境開發工具包(EDK),一種Linux主機或PCIe Gen5主機

PPOE和光纖電纜

PCIe 配置與硬件設置

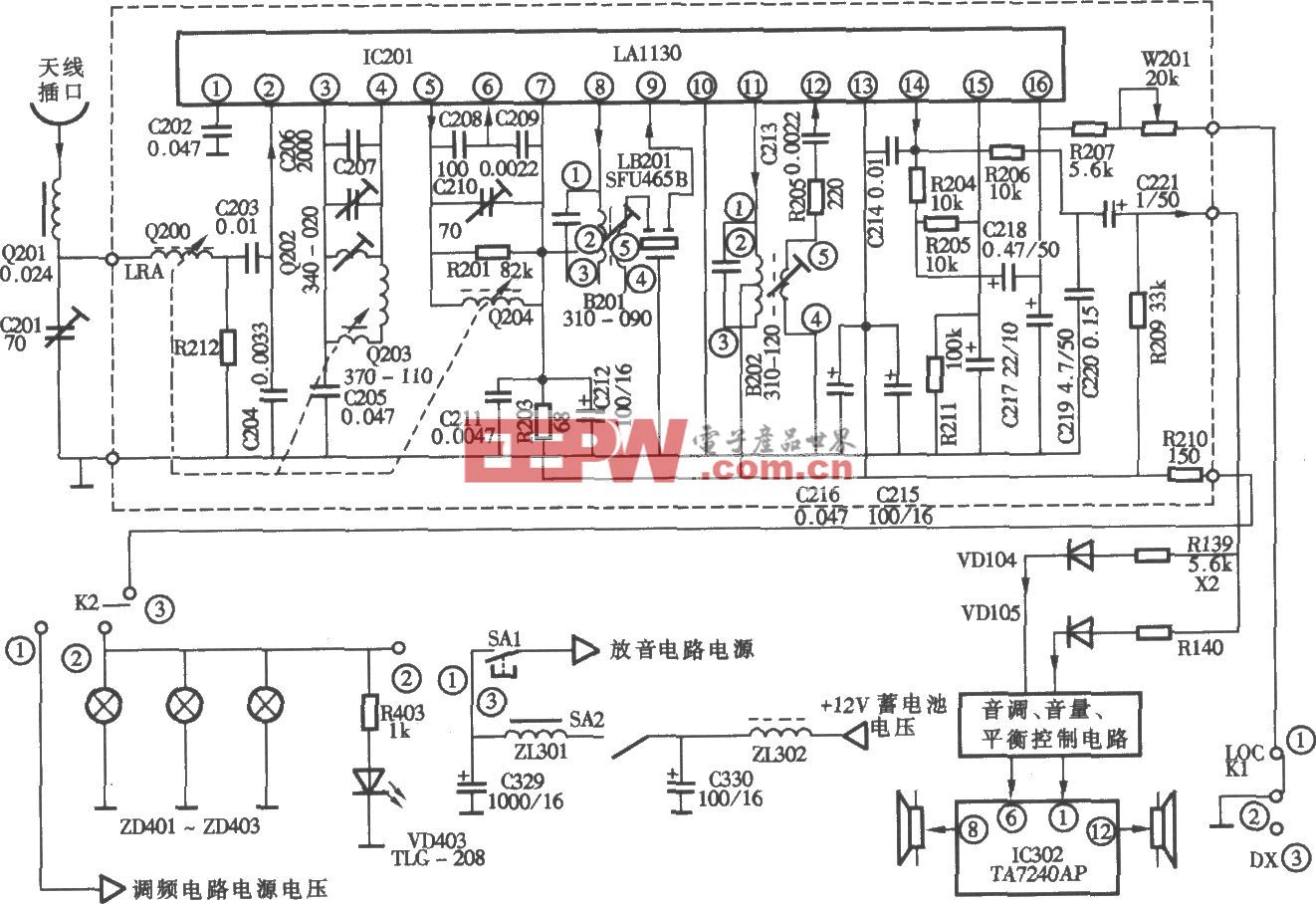

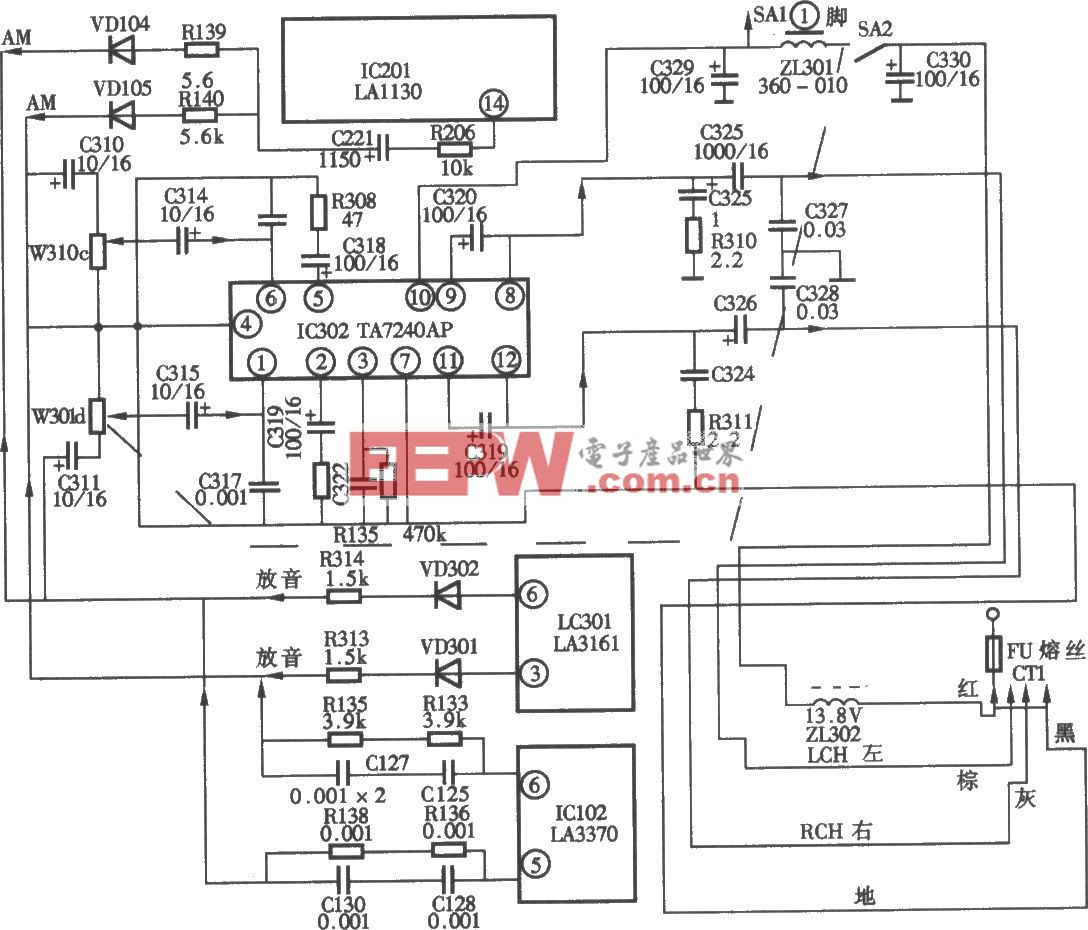

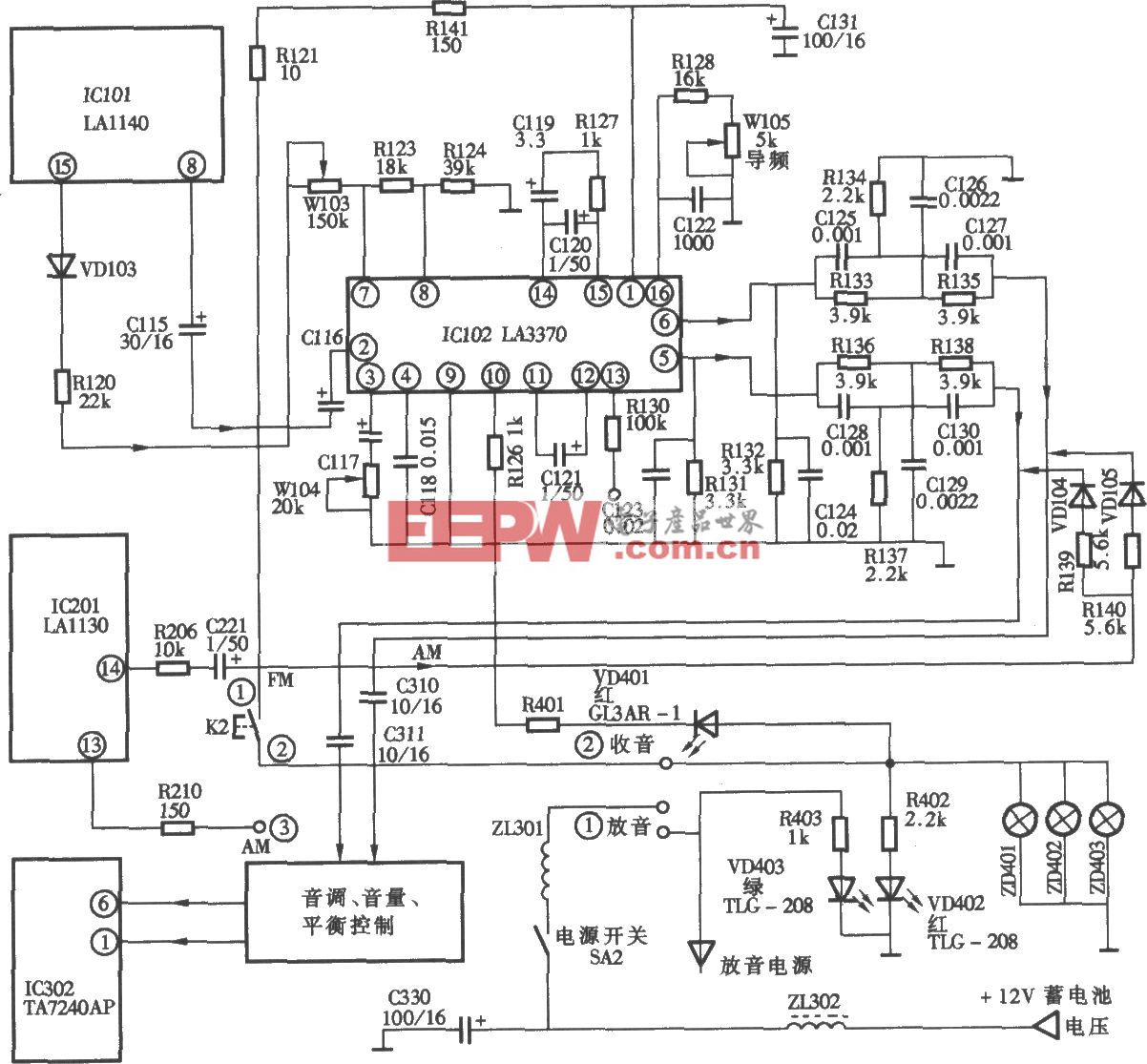

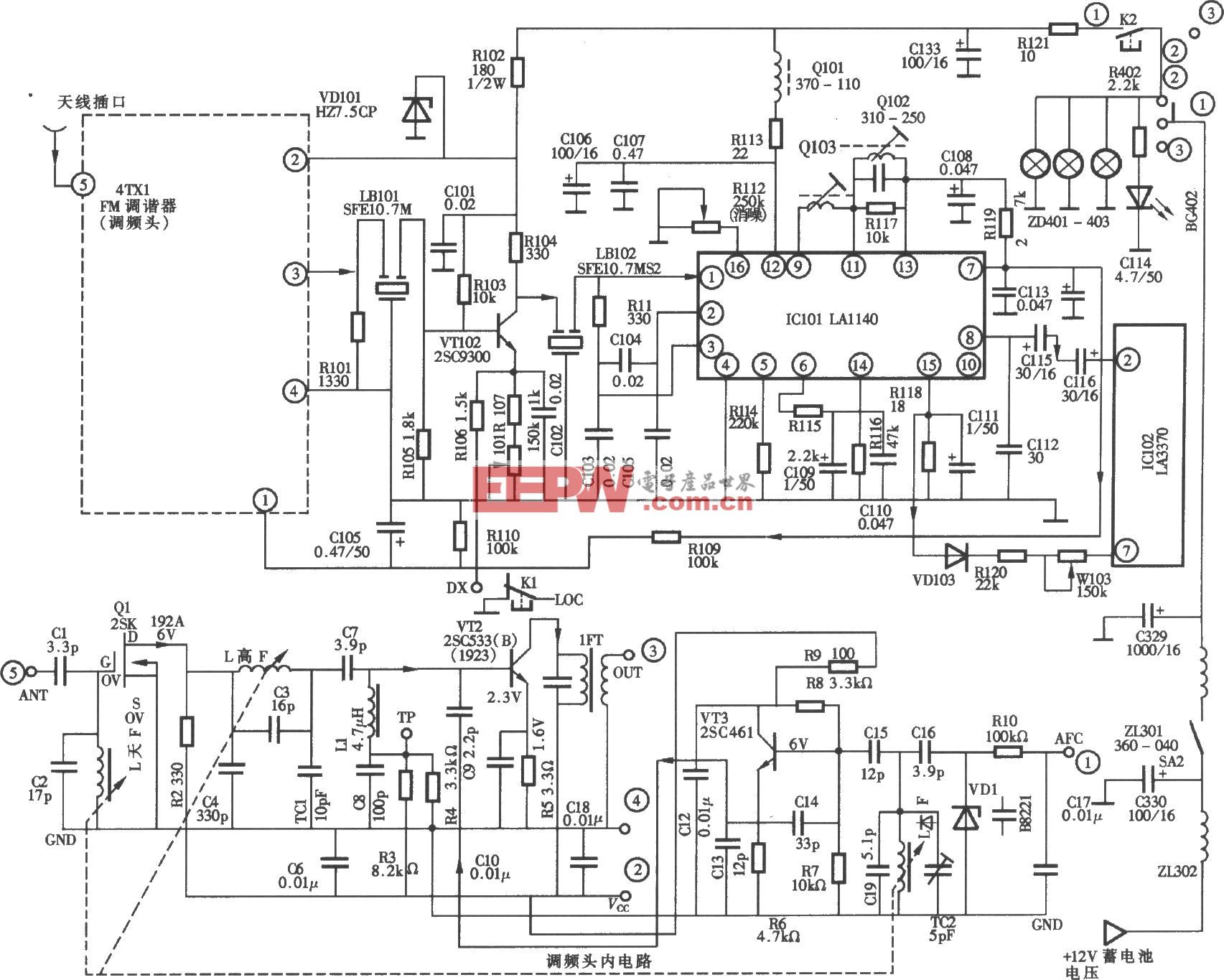

在開始安裝硬件之前,了解PCIe配置非常重要。這里的例子包括一個Linux或PCIe Gen5主機(EDK)和四個SSD目標。第五代我用了16條通道,支持32 Gb/s的數據速率。圖中展示了完整的安裝過程。這種配置可能會根據設計而變化。

這一設置展示了模擬器調試問題相較于FPGA原型的優勢,凸顯了仿真環境帶來的更高可見性和靈活性。

在設計中,我們需要一個模擬封裝文件,實例化PCIe IP設計和PCIe Gen5虛擬SpeedBridge。PCIe IP 支持EP和RC模式。在EP模式下,Linux主機(EDK)是根復合體,IP是端點;它使用全部16條通道進行數據傳輸。在RC模式下,IP(鈀撯模擬器)是一個根復合體,四個SSD是終端。

因此,我們需要五個PCIe SpeedBridges實例——一個用于EP模式(16通道),四個用于RC模式。每個 SpeedBridge 的遙控模式實例都支持四條車道。

Palladium 模擬器包含用于模擬器與 SpeedBridge 之間通信所需的 TPOD。TPOD是模擬器上的端口,由電源端口和數據端口組成。電源端口為連接的SpeedBridges供電,光纖電纜傳輸數據。由于PCIe主機和SSD目標需要五個SpeedBridge,因此必須啟用五個TPOD。

鈀金仿真包含兩個步驟:編譯和合成;以及管理工作。

第一步有兩種模式可選:

電路內仿真(ICE)模式/遺留模式,僅將可綜合設計編譯、合成并加載到模擬器中。不可綜合部分,如UVM測試平臺/系統任務,僅在IB主機上運行。IB 鏈路用于將交易導入模擬器。

通過IXCOM流程實現仿真加速(SA)模式,將不可綜合和可合成設計編譯、合成并下載到模擬器中。不可綜合部分包括文件處理、初始語句、斷言以及 Verilog/System Verilog HDL 支持的系統任務。

設計必須在Palladium上編譯和合成,Palladium中使用IXCOM流程,因為它包含不可綜合的結構,如文件處理和系統任務,這些都被下載到模擬器中。為了運行該作業,需要一個獨立的仿真環境。請參閱 Cadence 官網,因為仿真流程包含 Cadence 專有信息。

調試Palladium仿真器上的PCIe設計

假設仿真流程已開發完成,仿真器已準備好用于測試PCIe IP和軟件。以下場景描述了一些調試技術:

假設Palladium模擬器處于RC模式,四個SSD目標是終端。在這里,RC無法與任何SSD目標建立聯系。導致這種失敗有兩種可能。設計本身存在漏洞,或者軟件沒有生成合適的訓練序列。在這種情況下,鈀金提供了一種非常強大的技術,可以在運行時探測設計信號并生成波形。優點是無需重新合成設計,因為整個或部分設計可以通過探測轉化為波形。如果RTL運行正常,那么必須對軟件進行潛在問題的調查。

如果設計正常,能與三個SSD目標建立連接,但無法與第四個目標連接,則調查該目標并進行斷電重啟。斷電重啟意味著將電源線和光纖電纜拔插并重新插入故障的SpeedBridge。如果還是不行,那就換速度新娘或線纜再試一次。如果還是不行,Cadence會幫忙調試這個問題。

考慮端點模式的鈀,EDK是宿主或根復合體。雖然 EDK 啟動,但它會與端點建立鏈接。可能是在讀取端點配置寄存器時發生,EDK沒收到TLP導致超時。這會導致EDK卡住,需要斷電重啟才能恢復正常狀態。這是因為RTL端點模式出現了bug,或者EDK卡住并無法接收端點發送的TLP。或者軟件給了端點錯誤的信息,設計中不支持這一點。同樣,信號可以在不重新合成設計的情況下探測,并生成波形來調查問題。

一旦在RTL中發現漏洞,必須重新合成并在Palladium上實現該設計以測試修復。除非加入了大功能,否則重合成通常會使時鐘頻率增加幾千赫茲。在這里,SpeedBridges將通過進行速率調整來確保數據完整性,并保持設計性能。

鈀金上的再合成不需要滿足時間安排、應用定位約束和耗時的實施策略。編譯器將確定工作時鐘頻率,SpeedBridge通過速率調整確保其性能。該設計可在運行時調試,因此對鈀金的調試效率高。

在基于FPGA的平臺上調試PCIe設計

在FPGA上實現PCIe設計超出本文范圍。假設所需的硬件、PCIe IP和軟件都已實現,FPGA綜合和PNR(布局與路由)流程也已可用。關于FPGA流程中的調試方面,以下場景描述了基于FPGA平臺的調試技術:

以上述相同例子為例,PCIe無法枚舉四個SSD目標。為了調試問題,必須探測設計以生成波形。信號可以通過集成邏輯分析儀(ILA)/芯片示波器進行探測,但需要保留信號以防止優化。設計必須在帶有額外儀器邏輯的FPGA上綜合并實現,以便ILA需要額外儀器邏輯。探測到ILA和儀器邏輯的信號需要相同的時鐘來捕獲數據。例如,如果PCIe信號在100M頻率下工作,那么ILA邏輯也需要100M時鐘。因此,為了探測調試信號,FPGA設計者還必須滿足設計與ILA邏輯之間的時序。如果探測信號不足以調試設計,那么FPGA設計和實現循環將繼續,直到發現并修復錯誤。

另一種可用的FPGA原型工具是Protium仿真器,這是一種基于FPGA的仿真器。Protium上的PCIe配置類似于Palladium,變化不大,但超出本文范圍。要用Protium探測信號生成波形,必須保留信號,并在腳本中施加觸發。它需要在Protium模擬器上重新合成并重新實現設計,并啟用觸發信號。探測信號所需的儀器邏輯由Protium CAD工具自動實現。因此,Protium的設計和實現周期會持續,直到發現并修復該漏洞。

顯而易見的是,在FPGA平臺上調試是一個充滿挑戰且耗時的過程。整個設計必須實現以生成波形,這涉及滿足時序限制并成功將設計部署到FPGA上。顯然,基于FPGA的調試效率低于基于鈀的調試方法。

高級仿真是最佳調試路徑

有效的驗證和調試對于確保PCIe Gen5系統的可靠性和性能至關重要,而PCIe Gen5系統是現代計算中高速數據傳輸的核心。像Palladium這樣的平臺通過運行時信號探測和實時分析,提供了一種簡化高效的調試方法,顯著縮短了開發時間。

雖然基于FPGA的平臺提供了替代的驗證方法,但其復雜性和耗時性使得它們在迭代調試中效率較低。通過利用先進的仿真工具和方法,工程師可以優化設計流程,及早發現問題,并確保PCIe Gen5協議在復雜系統中的無縫集成。

評論